# TEXAS INSTRUMENTS

# 9900

# TMS9918A/TMS9928A/TMS9929A Video Display Processors

MICROPROCESSOR SERIES™

#### **IMPORTANT NOTICES**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

Copyright © 1982 Texas Instruments Incorporated

#### **TABLE OF CONTENTS**

| SECTION | J                    | PA                                                           | AGE  |

|---------|----------------------|--------------------------------------------------------------|------|

| 1.      | INTR                 | ODUCTION                                                     | 1-1  |

|         | 1.1                  | Description                                                  | 1-1  |

|         | 1.2                  | Features                                                     |      |

|         | 1.3                  | Typical Applications                                         |      |

|         | 1.4                  | Acronyms and Glossary                                        |      |

|         |                      |                                                              |      |

| 2.      |                      | HITECTURE                                                    |      |

|         | 2.1                  | CPU Interface                                                |      |

|         |                      | 2.1.1 CPU Interface Control Signals                          |      |

|         |                      | 2.1.2 CPU Write to VDP Register                              |      |

|         |                      | 2.1.3 CPU Write to VRAM                                      |      |

|         |                      | 2.1.4 CPU Read from VDP Status Register                      |      |

|         |                      | 2.1.5 CPU Read from VRAM                                     |      |

|         |                      | 2.1.6 VDP Interrupt                                          |      |

|         |                      | 2.1.7 VDP Initialization                                     |      |

|         | 2.2                  | Write-Only Registers                                         |      |

|         |                      | 2.2.1 Register 0                                             |      |

|         |                      | 2.2.2 Register 1                                             |      |

|         |                      | 2.2.3 Register 2                                             |      |

|         |                      | 2.2.4 Register 3                                             |      |

|         |                      | 2.2.5 Register 4                                             |      |

|         |                      | 2.2.6 Register 5                                             | .2-7 |

|         |                      | 2.2.7 Register 6                                             | .2-/ |

|         |                      | 2.2.8 Register 7                                             | .2-7 |

|         |                      | 2.2.9 Setup Values for VDP Registers 2 through 6             |      |

|         | 2.3                  | Status Register                                              | 2-11 |

|         |                      | 2.3.1 Interrupt Flag (F)                                     |      |

|         |                      | 2.3.2 Coincidence Flag (C)                                   | 2-11 |

|         |                      | 2.3.3 Fifth Sprite Flag (5S) and Number                      | 2-11 |

|         | 2.4                  | Video Display Modes                                          | 2-12 |

|         |                      | 2.4.1 Graphics I Mode                                        | 2-1/ |

|         |                      | 2.4.2 Graphics II Mode                                       | 2-19 |

|         |                      | 2.4.3 Multicolor Mode                                        |      |

|         |                      | 2.4.4 Text Mode                                              |      |

|         |                      | 2.4.5 Sprites                                                | 2-25 |

|         |                      | 2.4.6 A Step-by-Step Approach to Create Patterns and Sprites | 2-29 |

| 3.      | VDP                  | INTERFACES AND OPERATION                                     | 3-1  |

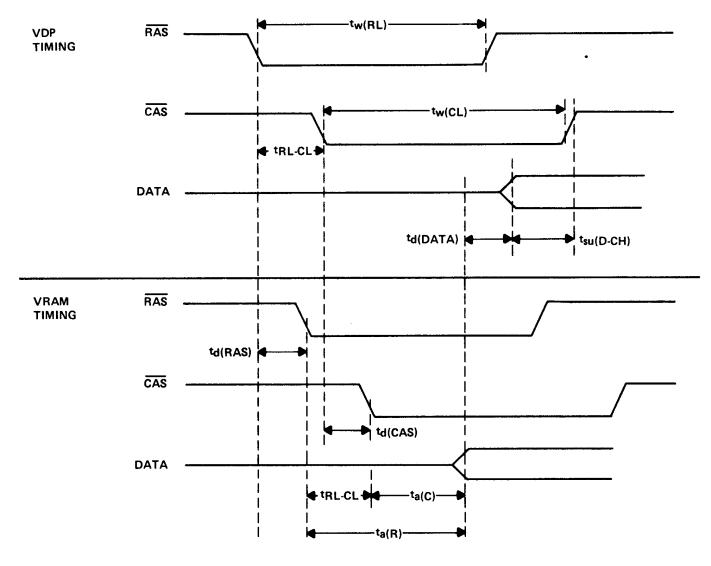

|         | 3.1                  | VDP/VRAM Interface                                           |      |

|         | 0                    | 3.1.1 VRAM Interface Control Signals                         | 3-1  |

|         |                      | 3.1.2 VRAM Memory Types                                      | .3-1 |

|         |                      | 3.1.3 VDP to DRAM Address Connections                        | .3-1 |

|         | 3.2                  | VRAM Memory Address Derivation                               | .3-3 |

|         | 3.3                  | VRAM Addressing Example                                      | .3-4 |

|         | 3.4                  | Monitor Interfaces                                           | .3-5 |

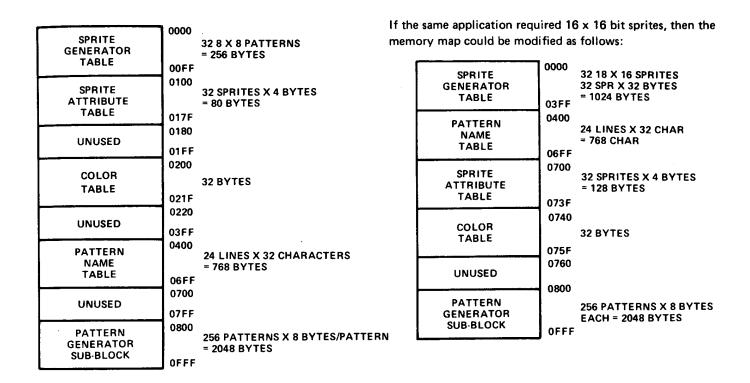

|         | <b>U</b> 1. <b>T</b> | 3.4.1 TMS9918A Monitor Interface                             | .3-5 |

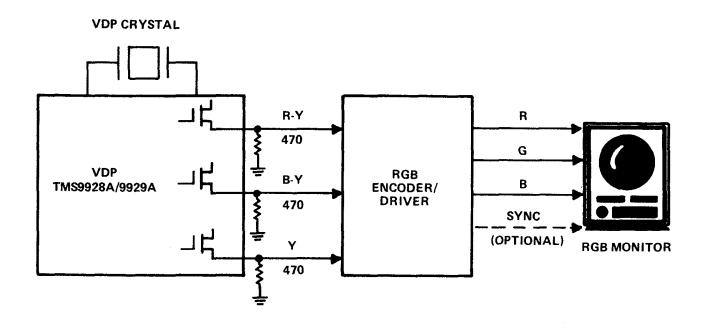

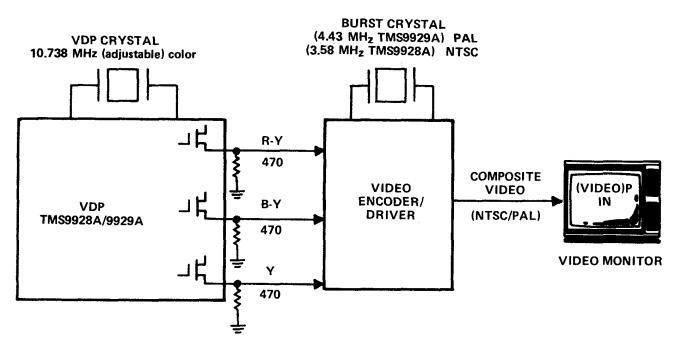

|         |                      | 3.4.2 TMS9928A/9929A Monitor Interface                       | .3-6 |

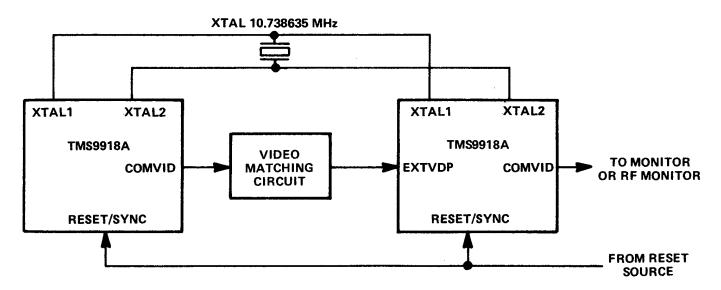

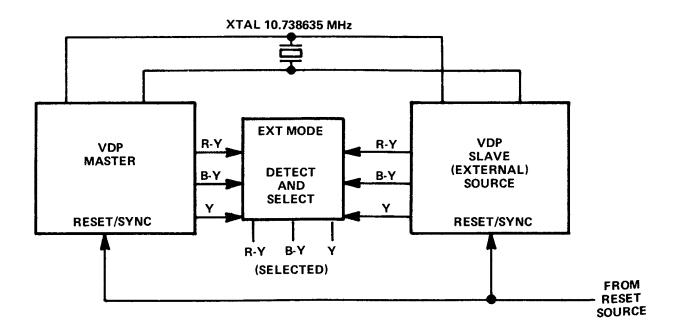

|         | 3.5                  | TMS9918A External VDP Operation                              |      |

|         | 3.6                  | Oscillator and Clock Generation                              | .3-8 |

|         |                      | 3.6.1 TMS9918A Color Phase Generation                        | .3-8 |

|         |                      | 3.6.2 Video Sync and Control Generation                      |      |

## **TABLE OF CONTENTS (continued)**

| SECTIO | N   | PAGE                                                                                                                                                                                                         |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 3.7 | VDP Terminal Assignments       3-9         3.7.1 TMS9918A Terminal Assignments       3-9         3.7.2 TMS9928A/9929A Terminal Assignments       3-11         3.7.3 TMS9918A/9928A/9929A Crystals       3-12 |

| 4.     | DEV | 'ICE APPLICATIONS4-1                                                                                                                                                                                         |

|        | 4.1 | VDP to TMS9900 Interface                                                                                                                                                                                     |

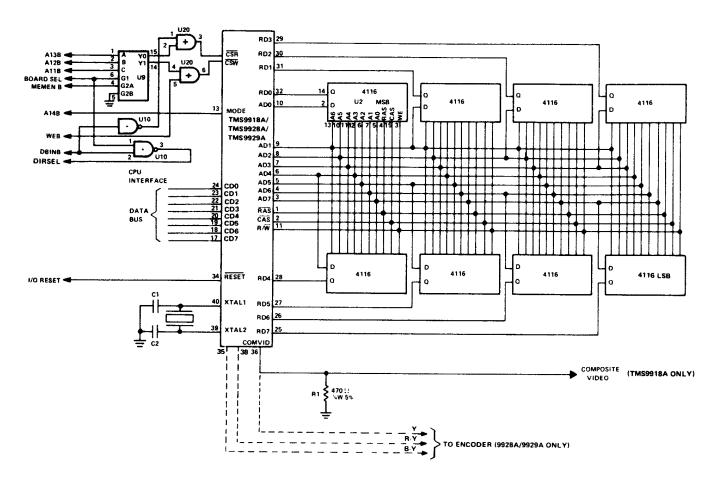

|        | 4.2 | TMS9918A/9928A/9929A Interface                                                                                                                                                                               |

|        |     | 4.2.1 TM990 (TMS9918A/9928A/9929A) Parts List                                                                                                                                                                |

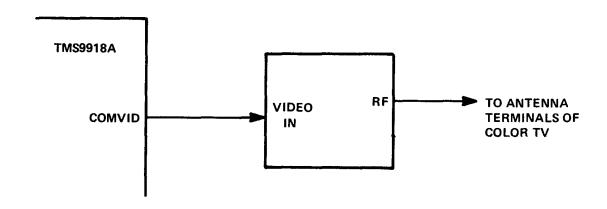

|        |     | 4.2.2 Composite Video Output                                                                                                                                                                                 |

|        |     | 4.2.3 Oscillator and Timing                                                                                                                                                                                  |

|        |     | 4.2.4 VRAM Connections                                                                                                                                                                                       |

|        | 4.3 | VDP Initialization                                                                                                                                                                                           |

|        | 4.4 | Typical Software Program                                                                                                                                                                                     |

|        |     | 4.4.1 General                                                                                                                                                                                                |

|        | 4.5 | TMS9900 Software SubRoutines                                                                                                                                                                                 |

| 5.     | TM: | S9918A/9928A/9929A ELECTRICAL SPECIFICATIONS                                                                                                                                                                 |

|        | 5.1 | Absolute Maximum Ratings5-1                                                                                                                                                                                  |

|        | 5.2 | Recommended Operating Conditions5-1                                                                                                                                                                          |

|        | 5.3 | Electrical Characteristics                                                                                                                                                                                   |

|        | 5.4 | Timing Requirements5-4                                                                                                                                                                                       |

|        | 5.5 | Switching Characteristics                                                                                                                                                                                    |

|        |     | LIST OF APPENDICES                                                                                                                                                                                           |

| APPEND | IX  | PAGE                                                                                                                                                                                                         |

|        | Α   | ASCII Character Set                                                                                                                                                                                          |

|        | В   | Choosing VRAM Memory                                                                                                                                                                                         |

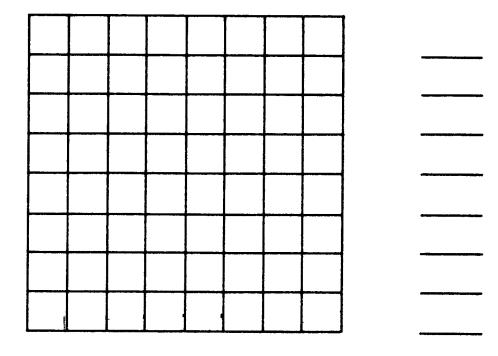

|        | Ċ   | Pattern and Screen Worksheets                                                                                                                                                                                |

#### LIST OF ILLUSTRATIONS

| IGURE |                                                                                                  | PAGE  |

|-------|--------------------------------------------------------------------------------------------------|-------|

| 1-1   | System Block Diagram                                                                             | 1-2   |

| 2-1   | VDP Block Diagram                                                                                | 2-2   |

| 2-2   | VDP to CPU Interface                                                                             | 2-3   |

| 2-3   | VDP Registers                                                                                    | 2-6   |

| 2-4   | VDP Display Planes (Definition)                                                                  |       |

| 2-5   | VDP Display Planes (First 32 Planes)                                                             | .2-13 |

| 2-6   | TMS9928A/9929A Signal Waveforms for Multiple VDP Operation                                       |       |

| 2-7   | Using Color Difference Signals to Mix External Color Difference Type Source                      |       |

| 2-8   | Using Color Difference Signals to Mix External Video Sources                                     |       |

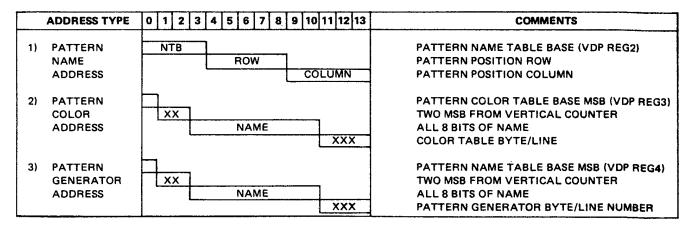

| 2-9   | Pattern Graphics Name Table Mapping                                                              |       |

| 2-10  | Graphics I Mode Mapping                                                                          |       |

| 2-11  | Pattern Display Mapping                                                                          |       |

| 2-12  | Graphics II Mode Mapping                                                                         |       |

| 2-13  | Pattern Display Mapping                                                                          |       |

| 2-14  | Multicolor List Mapping                                                                          |       |

| 2-15  | Multicolor Block Display                                                                         |       |

| 2-16  | Multicolor Mode Mapping                                                                          |       |

| 2-17  | Text Mode Name Table Pattern Positions                                                           |       |

| 2-18  | Mapping of VRAM into the Pattern Plane in Text Mode                                              |       |

| 2-19  | Sprite Attribute Table Entry                                                                     |       |

| 2-20  | Sprite Mapping                                                                                   |       |

| 2-21  | Size 1 Sprite Mapping                                                                            | .2-28 |

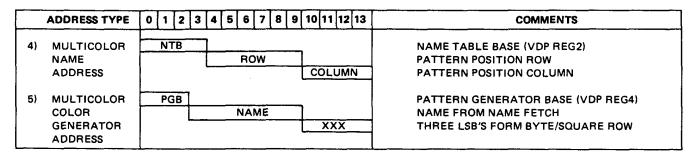

| 3-1   | VRAM Interface                                                                                   | 3 2   |

| 3-1   | VDP-VRAM Memory Allocation                                                                       |       |

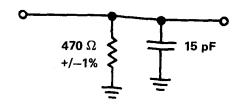

| 3-2   | Composite Video Pull-Down Circuit                                                                |       |

| 3-4   | Use of TMS9928A/9929A with Different Monitors                                                    |       |

| 3-5   | Cascading Two TMS9918A VDPs                                                                      |       |

| 3-6   | Cascading Two TMS9918A/9929A VDPs                                                                |       |

|       | Coscoding (Wo Thioso to A/3325 A VDI 3                                                           |       |

| 4-1   | Minimum System Interface to TMS9900                                                              | 1.1   |

| 4-2   | TMS9918A/9928A/9929A Interface                                                                   |       |

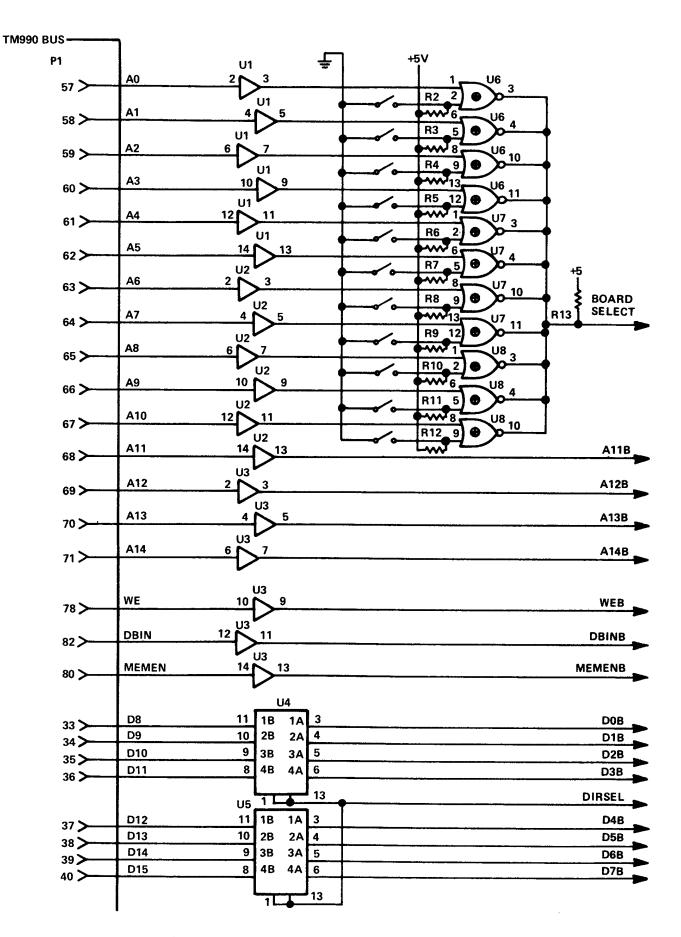

| 4-3   | TM990 (TMS9918A/9928A/9929A) Demo Board                                                          |       |

| 4-4   |                                                                                                  |       |

| 4-5   | RF Modulator Connection                                                                          |       |

| -     | External Frequency Source                                                                        |       |

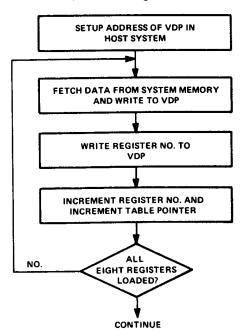

| 4-6   | VDP Register Initialization Procedure                                                            | 4-5   |

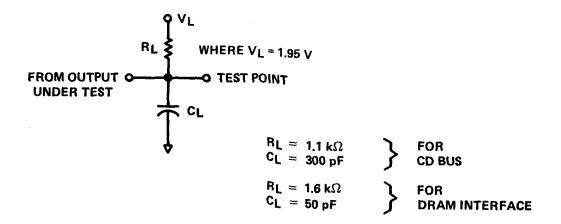

| 5-1   | Load Circuit for COMVID (All Devices) and R-Y, Y, B-Y Switching Characteristics (TMS9928A/9929A) | E 0   |

| 5-2   |                                                                                                  |       |

| 5-3   | Load Circuits for All Outputs Except COMVID, R-Y, Y, B-Y                                         |       |

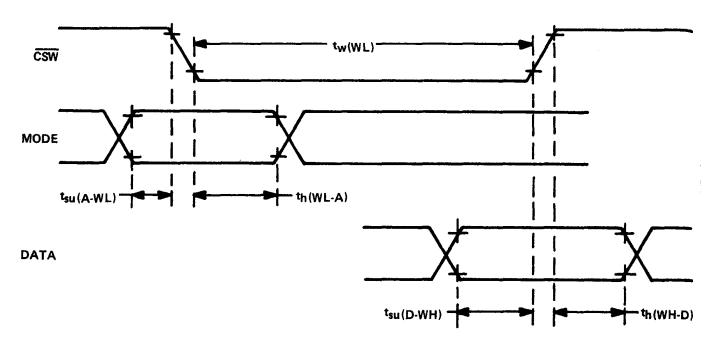

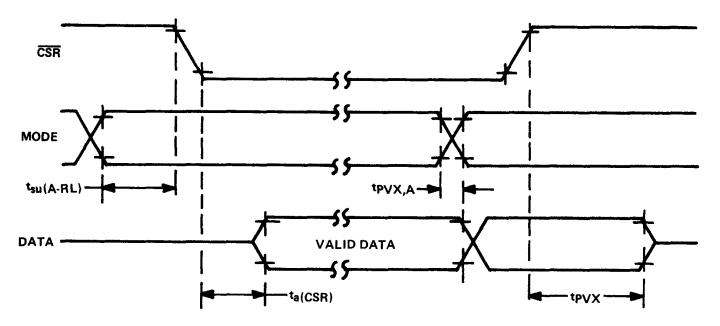

| _     | CPU-VDP Write Cycle (All Devices)                                                                |       |

| 5-4   | CPU-VDP Read Cycle (All Devices)                                                                 |       |

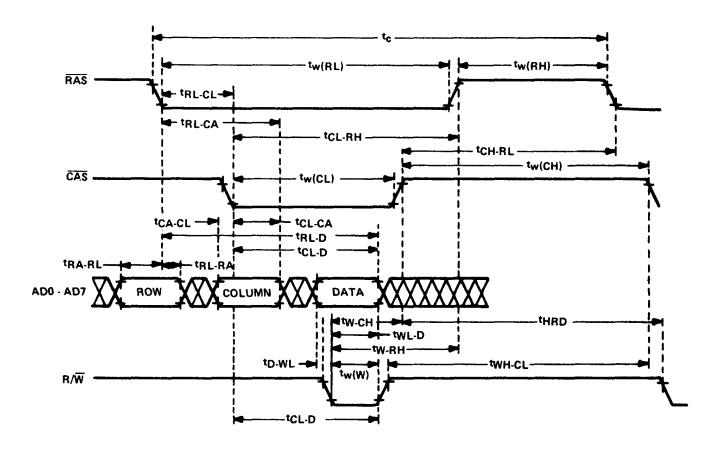

| 5-5   | VRAM Write Cycle                                                                                 |       |

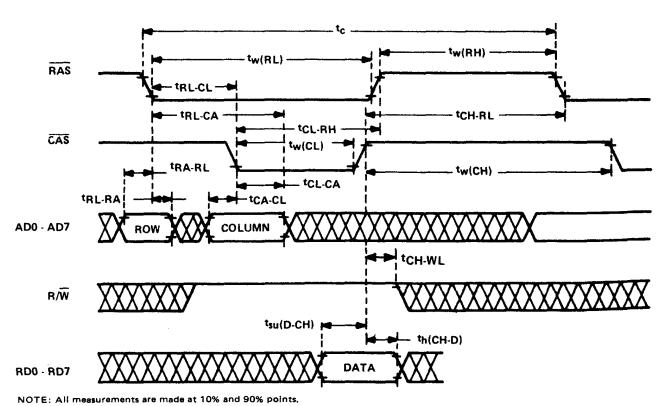

| 5-6   | VRAM Read Cycle                                                                                  |       |

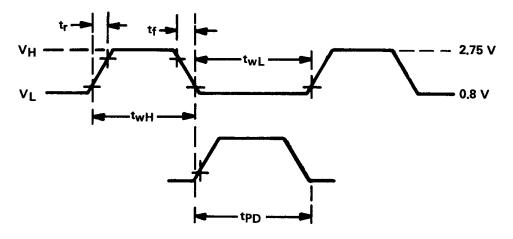

| 5-7   | External Clock Timing Waveform                                                                   |       |

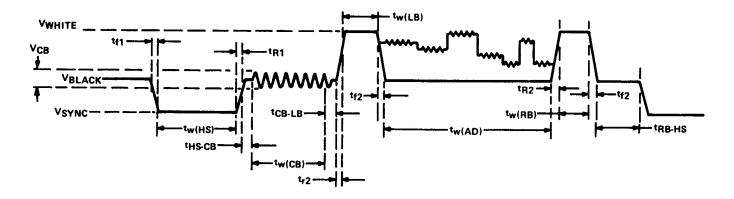

| 5-8   | TMS9918A COMVID Horizontal Timing                                                                | .5-12 |

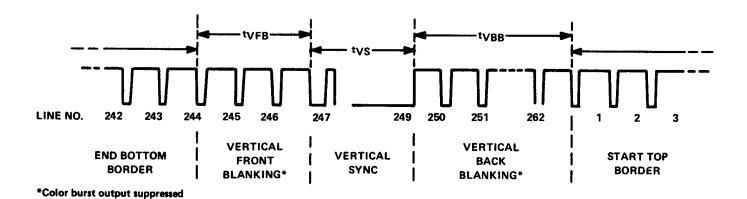

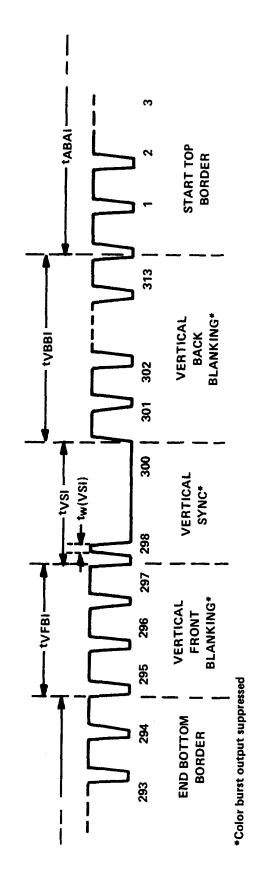

| 5-9   | TMS9918A Vertical Timing                                                                         | .5-12 |

# LIST OF ILLUSTRATIONS (continued)

| FIGUR                           | E .                                                                                                                                           | PAGE                 |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

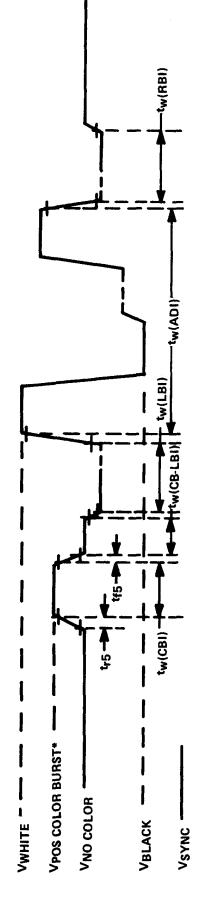

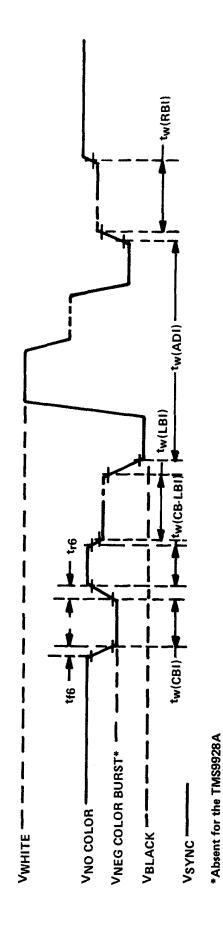

| 5-10<br>5-11<br>5-12<br>5-13    | TMS9928A/9929A Y Horizontal Timing . TMS9928A/9929A R-Y Horizontal Timing . TMS9928A/9929A B-Y Horizontal Timing . TMS9929A Vertical Timing . | 5-13<br>5-14         |

|                                 | LIST OF TABLES                                                                                                                                |                      |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5 | CPU/VDP Data Transfers  Memory Access Delay Times  Color Assignments  Graphics I Mode Color Table  Sprite Pattern Formats                     | .2-4<br>2-17<br>2-19 |

| 3-1<br>3-2<br>3-3               | VDP to DRAM Address Connections Pattern Graphics Address Location Tables Screen Display Parameters                                            | 3-3                  |

| 4-1                             | VDP Port Addresses for Figure 4-1                                                                                                             | 4-1                  |

#### 1. INTRODUCTION

#### 1.1 Description

The TMS9918A/9928A/9929A video display processors (VDP) are N-channel MOS LSI devices used in video systems where data display on a raster-scanned home color television set or color monitor is desired. These devices generate all necessary video, control, and synchronization signals and also control the storage, retrieval, and refresh of display data in the dynamic screen refresh memory. The interfaces to the microprocessor, refresh memory, and the TV require a minimum of additional electronics for the TMS9918A.

In Section 1.4, there is a list of acronyms and a glossary of terms used in this manual.

The TMS9928A/9929A VDPs are functionally identical to the TMS9918A except that the NTSC color encoding circuitry has been removed and replaced with luminance and color difference signals. The TMS9918A is pin-for-pin compatible with the TMS9928A/9929A, except for three pins, the composite video output, the external video input and the CPU clock output. These pins are replaced with the Black/White luminance and composite sync (Y) output and two color difference pins, Blue (B-Y) and Red (R-Y) outputs, respectively. The color difference outputs allow the user to generate Red-Green-Blue (R-G-B) drive for direct color gun control, or composite video for use with NTSC or PAL video color monitor. However, to connect these three outputs to a R-G-B or monitor requires additional R-G-B or encoder circuitry.

The TMS9918A/9928A have a 525-line format for U.S. televisions while the TMS9929A has a 625-line format for use with the European PAL system.

The VDP has four video display modes: Graphics I, Graphics II, Multicolor and Text mode. The Text mode provides twenty-four 40-character rows in two colors and is intended to maximize the capacity of the TV screen to display alphanumeric character. The Multicolor mode provides an unrestricted  $64 \times 48$  color-dot display employing 15 colors plus transparent. The Graphics I mode provides a  $256 \times 192$  pixel display for generating pattern graphics in 15 colors plus transparent. The Graphics II mode is an enhancement of Graphics I mode, allowing it to generate more complex color and pattern displays. The four video display modes are described in detail in Section 2.4.

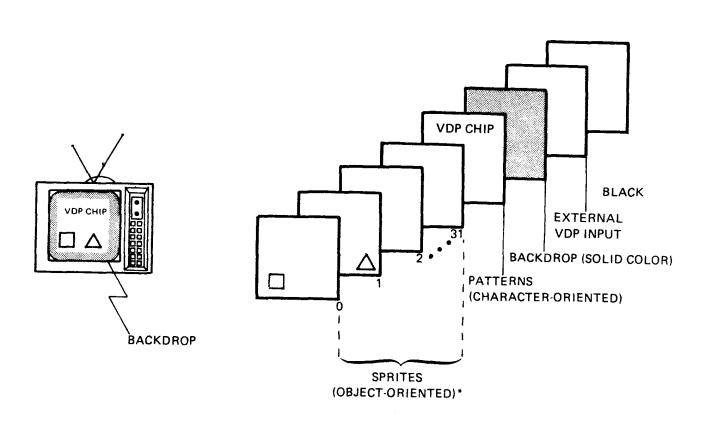

The video display consists of 35 planes: external VDP, backdrop, pattern plane, and 32 Sprite Planes. The planes are vertically stacked with the external VDP being the bottom or innermost plane. The backdrop plane is the next plane followed by the pattern plane that contains Graphics I and Graphics II patterns with the 32 Sprite Planes as the top planes.

The TMS9918A/9928A/9929A VDPs use either a 4K, 8K, or 16K-type low-cost dynamic memory (TMS4027, TMS4108, TMS4116) for storage of the display parameters.

The TMS9918A, TMS9928A, and TMS9929A interface identically to the host microprocessor making them software compatible. Thus, all references to VDP in this document apply to all three devices, except where noted.

#### 1.2 FEATURES

- Single-chip solution for interfacing color TVs (excluding Random-Access Memory (RAM) and Radio Frequency (RF) modulator (TMS9918A only)

- 256 × 192 resolution on TV screen

- 15 unique colors plus transparent

- General 8-bit bidirectional interface to Central Processor Unit (CPU)

- Direct wiring to 4K, 8K, or 16K dynamic RAM memories

- Automatic and transparent refresh of dynamic RAMs

- Multiple VDP systems capability

- External VDP input capability (TMS9918A only)

- Composite video output (TMS9918A only)

- Unique planar representation for 3D simulation

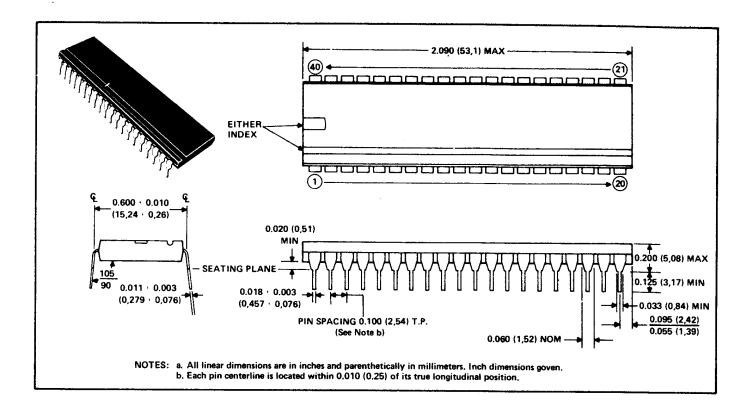

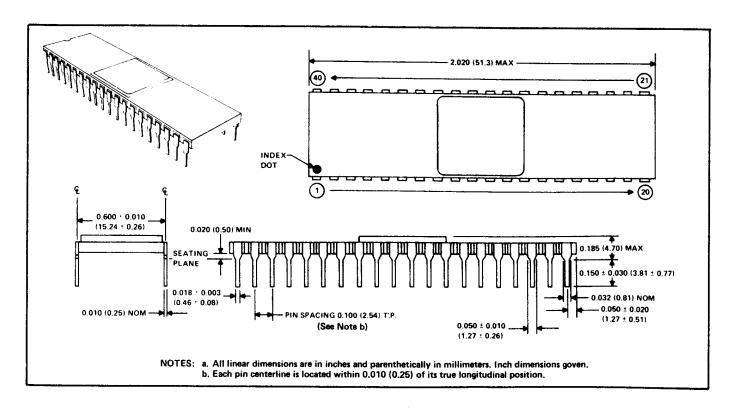

- Standard 40-pin package

- Color difference outputs allow RGB drive TMS9928A/9929A

#### 1.3 TYPICAL APPLICATIONS

- Color computer terminals

- Home computers

- Drafting/design aids

- Teaching aids

- Industrial process monitoring

- Home educational systems

- Animation aids

- European 625-line TV (TMS9929A only)

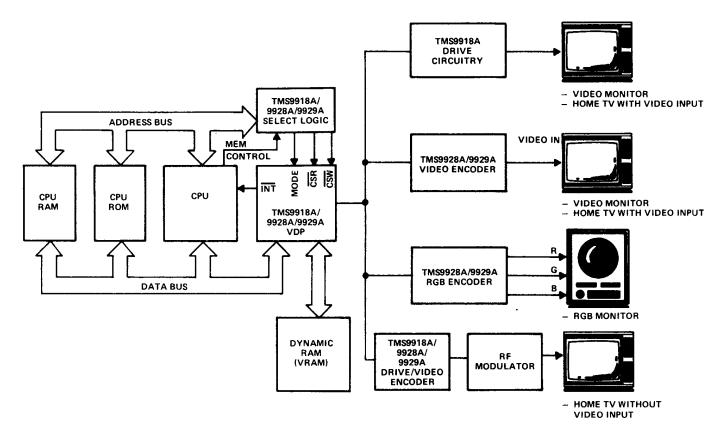

The following example of a typical application may help introduce the user to the TMS9918A VDP. Figure 1-1 is a block diagram of a typical application. Each of the concepts presented in the example is described more fully in later sections of this manual.

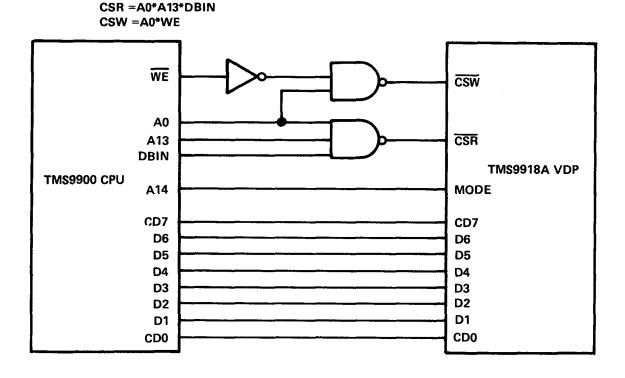

FIGURE 1-1 - SYSTEM BLOCK DIAGRAM

The VDP basically has three interfaces: CPU, color monitor, and dynamic refresh RAM (VRAM), the contents of which define the TV image. The TMS9918A also has eight write-only registers and a read-only status register.

The VDP communicates with the CPU via an 8-bit bidirectional data bus. Three control lines, decoded from the CPU address and enable lines, determine interpretation of the bus. Through the bus, the CPU can write to VRAM, read from VRAM, write to VDP registers, and read the VDP status. The VDP also generates an interrupt signal after every refresh of the TV display.

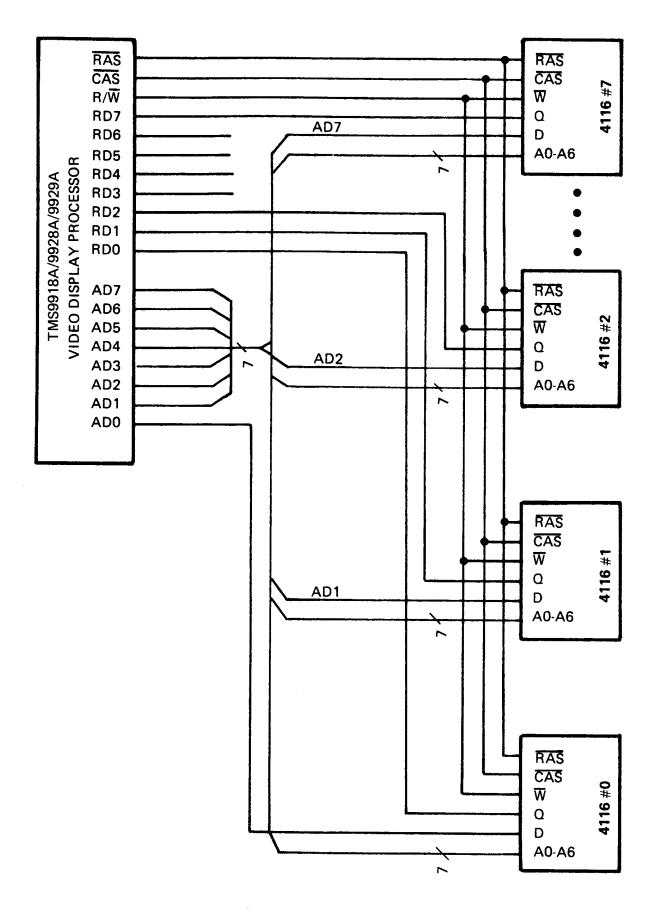

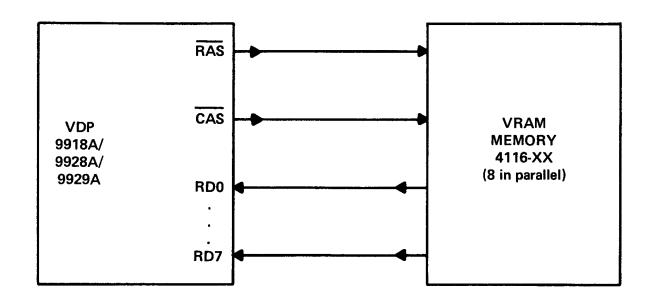

The dynamic RAM interface consists of direct wiring of eight 4K  $\times$  1, 8K  $\times$  1, or 16K  $\times$  1 dynamic RAS/CAS-type RAMs to the VDP. The amount of RAM required is dependent upon the features selected for use in the application.

The interface to the monitor can consist of either wiring the TMS9918A's composite video output pin (suitably buffered) to the input of a color or black-and-white monitor, or using an appropriate RF modulator to feed the signal into a TV antenna terminal. The TMS9928A/9929A require additional encoder circuitry to interface to a RGB or to a composite video monitor.

The VDP operates in four modes, and each one can affect the way the VRAM is mapped onto the television screen. In Graphics I and II modes, characters are mapped onto the screen in  $8\times8$  pixel blocks, yielding 24 lines of 32 blocks (pattern positions) each. In Text mode, there are 24 lines of 40 blocks, each of which is  $6\times8$  pixels. In Multicolor mode, there are 48 lines of 64 blocks, each of which is composed of  $4\times4$  picture elements (pixels), all of one solid color. In addition to these, sprites can be superimposed onto the television image in Graphics I, II, and Multicolor mode. Furthermore, signals entering the TMS9918A through the external VDP input can be used as a background to the TMS9918A.

#### **ACRONYMS AND GLOSSARY**

B-Y Blue color difference output

COMVID Contains luminance, chrominance and all sync pulse necessary for horizontal and vertical timing

(Composite Video)

CAS Column Address Strobe

CPU Central Processor Unit

CSR CPU from VDP read select

CSW CPU to VDP write select

CPUCLK XTAL = 3 GROMCLK XTAL = 24

LSB Least Significant Bit

LSI Large Scale Integration

MOS Metal Oxide Semiconductor

MHz Megahertz

MSB Most Significant Bit

NTSC National Television Standards Committee which specifies television signal standards for the USA

PAL Phase Alternating Line

Pixel Picture Element - the smallest point on the TV screen that can be independently controlled.

RAM Random-Access Memory

RAS Row-Address Strobe

RASTER The area in which an image is reproduced

RF Radio Frequency

R-G-B Red-Green-Blue

ROM Read-Only Memory

R/W Read/Write

R-Y Red color difference output

Sprite An object whose pattern is relative to a specified X,Y coordinate and whose position can therefore

be controlled by that coordinate with a positional resolution of one pixel

VDP Video Display Processor

VRAM Video RAM; refers to the dynamic RAMs that connect to the VDP and whose contents define the TV

image

Y Black/white luminance and composite sync

#### 2. ARCHITECTURE

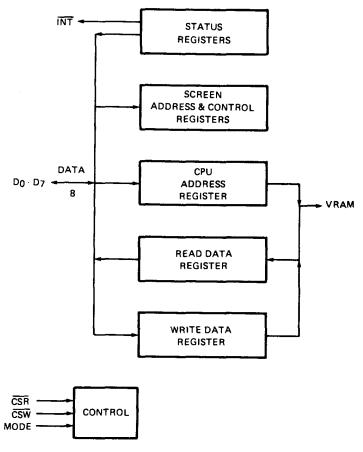

The TMS9918A video display processor (VDP) is designed to provide a simple interface between a microprocessor and a raster-scanned color television. The TMS9928A/9929A VDPs are designed as a simple interface between a microprocessor, and R-G-B monitor or video encoder which produces the video for a video monitor. Figure 2-1 is a block diagram of the major portions of the VDP architecture interfaces to the VDP, CPU, VRAM, and color television.

#### 2.1 CPU INTERFACE

The VDP interface to the CPU using an 8-bit bidirectional data bus, three control lines, and an interrupt is shown in Figure 2-2. Through this interface the CPU can conduct four operations:

- (1) Write data bytes to VRAM

- (2) Read data bytes from VRAM

- (3) Write to one of the eight VDP write-only registers

- (4) Read the VDP Status Register.

Each of these operations requires one or more data transfers to take place over the CPU/VDP data bus interface. The interpretation of the data transfer is determined by the three control lines of the VDP.

#### NOTE

The CPU can communicate with the VDP simultaneously and asynchronously with the VDP's TV screen refresh operations. The VDP performs memory management and allows periodic intervals of CPU access to VRAM even in the middle of a raster scan.

#### 2.1.1 CPU Interface Control Signals

The type and direction of data transfers are controlled by the CSW, CSR, and MODE inputs. CSW is the CPU to VDP write select. When it is active (low), the eight bits on CD0-CD7 are strobed into the VDP. CSR is the CPU from VDP read select. When it is active (low), the VDP outputs eight bits on CD0-CD7 to the CPU. CSW and CSR should never be simultaneously low at the same time. If both are low, the VDP outputs data on CD0-CD7 and latches in invalid data.

MODE determines the source or destination of a read or write data transfer. MODE is normally tied to a CPU low order address line (A14 for TMS9900).

#### 2.1.2 CPU Write to VDP Register

The VDP has eight write-only registers and one read-only status register. The write-only registers control the VDP operation and determine the way in which VRAM is allocated. The status register contains interrupt, sprite coincidence and fifth sprite status flags.

Each of the eight VDP write-only registers can be loaded using two 8-bit data transfers from the CPU. Table 2-1 describes the required format for the two bytes. The first byte transferred is the data byte, and the second byte transferred controls the destination. The MSB of the second byte must be a 1. The next four bits are 0s, and the lowest three bits make up the destination register number. The MODE input is high for both byte transfers.

To rewrite the data in an internal register after a byte of data has already been loaded, the status register must be read so that internal CPU interface logic is reinitialized and will accept the next byte as data and not as a register destination. This situation may be encountered in interrupt-driven program environments. Whenever the status of VDP write parameters is in question, this procedure should be used.

#### NOTE

The CPU address is destroyed by writing to the VDP register.

TMS9918A

FIGURE 2-1 — VDP BLOCK DIAGRAM

FIGURE 2-2 — VDP TO CPU INTERFACE

#### 2.1.3 CPU Write to VRAM

The CPU transfers data to the VRAM through the VDP using a 14-bit autoincrementing address register. The address register setup requires 2-byte transfers. A 1-byte transfer is then required to write the data to the addressed VRAM byte. The address register is then autoincremented. Sequential VRAM writes require only 1-byte transfers since the address register is already set up. During setup of the address register, the two MSBs of the second address byte must be 0 and 1 respectively. MODE is high for both address transfers and low for the data transfer. CSW is used in all transfers to strobe the 8 bits into the VDP. See Table 2-1.

TABLE 2-1 - CPU/VDP DATA TRANSFERS

|                        | 1              |                |                | В              | IT              | <del></del>     |                 |                 | T   | T   | T    |

|------------------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----|-----|------|

| OPERATION              | 0_             | 1              | 2              | 3              | 4               | 5               | 6               | 7               | CSW | CSR | MODE |

| WRITE TO VDP REGISTER  |                |                |                | ·              |                 |                 |                 |                 |     |     |      |

| BYTE 1 DATA WRITE      | Do             | D <sub>1</sub> | $D_2$          | D <sub>3</sub> | D <sub>4</sub>  | D <sub>5</sub>  | $D_6$           | D <sub>7</sub>  | 0   | ] 1 | 1    |

| BYTE 2 REGISTER SELECT | 1              | 0              | 0              | 0              | 0               | RS <sub>0</sub> | RS <sub>1</sub> | RS <sub>2</sub> | 0   | 1   | 1    |

| WRITE TO VRAM          |                |                |                |                |                 |                 |                 |                 |     |     |      |

| BYTE 1 ADDRESS SETUP   | A6             | Α7             | Ag             | Ag             | A <sub>10</sub> | A <sub>11</sub> | A <sub>12</sub> | A <sub>13</sub> | 0   | 1   | 1    |

| BYTE 2 ADDRESS SETUP   | 0              | 1              | Αo             | Α1             | A <sub>2</sub>  | A <sub>3</sub>  | A <sub>4</sub>  | A <sub>5</sub>  | 0   | 1   | 1    |

| BYTE 3 DATA WRITE      | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub>  | D <sub>5</sub>  | D <sub>6</sub>  | D <sub>7</sub>  | 0   | 1   | 0    |

| READ FROM VDP REGISTER |                |                |                |                |                 |                 |                 |                 |     |     |      |

| BYTE 1 DATA READ       | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub>  | D <sub>5</sub>  | D <sub>6</sub>  | D <sub>7</sub>  | 1   | 0   | 1    |

| READ FROM VRAM         |                |                |                |                |                 |                 |                 |                 |     |     |      |

| BYTE 1 ADDRESS SETUP   | A <sub>6</sub> | A7             | Ag             | Ag             | A10             | A <sub>11</sub> | A12             | A13             | 0   | 1   | 1    |

| BYTE 2 ADDRESS SETUP   | o              | o              | Αo             | Α1             | A <sub>2</sub>  | A3              | A4              | A <sub>5</sub>  | 0   | 1   | 1    |

| BYTE 3 DATA READ       | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub>  | D <sub>5</sub>  | D <sub>6</sub>  | D <sub>7</sub>  | 1   | 0   | 0    |

#### 2.1.4 CPU Read from VDP Status Register

The CPU can read the contents of the status register with a single-byte transfer. MODE is high for the transfer. CSR is used to signal the VDP that a read operation is required.

#### 2.1.5 CPU Read from VRAM

The CPU reads from the VRAM through the VDP using the autoincrementing address register. A 1-byte transfer is then required to read the data from the addressed VRAM byte. The address register is then autoincremented. Sequential VRAM data reads require only a 1-byte transfer since the address register is already set up. During setup of the address register, the two MSBs of the second address byte must be 0. By setting up the address this way, a read cycle to VRAM is initiated and read data will be available for the first data transfer to the CPU. (See Table 2-1). MODE is high for the address byte transfers and low for the data transfers. The VDP requires approximately 8 microseconds to fetch the VRAM byte following the last data transfer and 2 microseconds following address setup.

The CPU interacts with VRAM memory through the VDP. The amount of time necessary for the CPU to transfer a byte of data to or from VRAM memory can vary from 2 to 8 microseconds. Once the VDP has been told to read or write a byte of data to or from VRAM it takes approximately 2 microseconds until the VDP is ready to make the data transfer. In addition to this 2 microsecond delay, the VDP must wait for a CPU access window; i.e., the period of time when the VDP is not occupied with memory refresh or screen display and is available to read or write data.

The worst case time between windows occurs during the Graphics I or Graphics II mode when sprites are being used. During the active display, CPU windows occur once every 16 memory cycles giving a maximum delay of 6 microseconds (a memory cycle takes about 372 nanoseconds). In the Text mode the CPU windows occur at least once out of every three memory cycles or a worst case delay of about 1.1 microseconds. Finally, in the Multicolor mode, CPU windows occur at least once out of every four memory cycles.

If the user needs to access memory in 2 microseconds, two situations occur where the time waiting for an access window is effectively zero. Both of these are independent of the display mode being used.

The first situation occurs when the blank bit of register 1 is 0. With this bit low, the entire screen will show only border color and the VDP does not have to wait for a CPU access window at any time.

The second situation occurs when the VDP is in the vertical refresh mode. The VDP issues an interrupt output at the end of each active area. This signal indicates that the VDP is entering the vertical refresh mode and that for the next 4.3 milliseconds there is no waiting for an access window. If the user wants the CPU to access memory during this interval, it is necessary for the controlling CPU to monitor the interrupt output of the VDP (the CPU can either poll this output or use it as an interrupt input).

The program that monitors the interrupt output must allow for its own delays in responding to the interrupt signal and recognize how much time it has left during the 4300 microsecond refresh period. The CPU must write a 1 to the interrupt enable bit of Register 1 in order to enable the interrupt for each frame, and then read the status register each time an interrupt is issued to clear the interrupt output. A summary of these delay times is presented in Table 2-2.

| CONDITION                                  | MODE              | VDP<br>DELAY | TIME WAITING FOR AN ACCESS WINDOW | TOTAL<br>TIME |

|--------------------------------------------|-------------------|--------------|-----------------------------------|---------------|

| Active Display Area                        | Text              | 2 μs         | 0 - 1.1 μs                        | 2 - 3.1 μs    |

| Active Display Area                        | Graphics<br>I, II | 2 µs         | 0 - 5.95 μs                       | 2 - 8 µs      |

| 4300 µs after Vertical<br>Interrupt Signal | All               | 2 μs         | 0 μs                              | 2 μs          |

| Register I<br>Blank Bit 0                  | Ail               | 2 μs         | 0 μs                              | 2 µs          |

| Active Display Area                        | Multicolor        | 2 μs         | 0 - 1.5 μs                        | 2 - 3.5 µs    |

TABLE 2-2 — MEMORY ACCESS DELAY TIMES

#### 2.1.6 VDP Interrupt

The VDP INT output pin is used to generate an interrupt at the end of each active-display scan, which is about every 1/60 second for the TMS9918A/9928A and 1/50 second for the TMS9929A. The INT output is active when the Interrupt Enable bit (IE) in VDP Register 1 is a 1 and the F bit of the status register is a 1. Interrupts are cleared when the status register is read.

#### 2.1.7 VDP Initialization

The VDP is externally initialized whenever the RESET input is active (low) and must be held low for a minimum of 3 microseconds. The external reset synchronizes all clocks with its falling edge, sets the horizontal and vertical counters to known states, and clears VDP registers 0 and 1. The video display is automatically blanked since the BLANK bit in VDP register 1 becomes a 0. The VDP, however, continues to refresh the VRAM even though the display is blanked. While the RESET line is active, the VDP does not refresh the VRAM.

#### 2.2 WRITE-ONLY REGISTERS

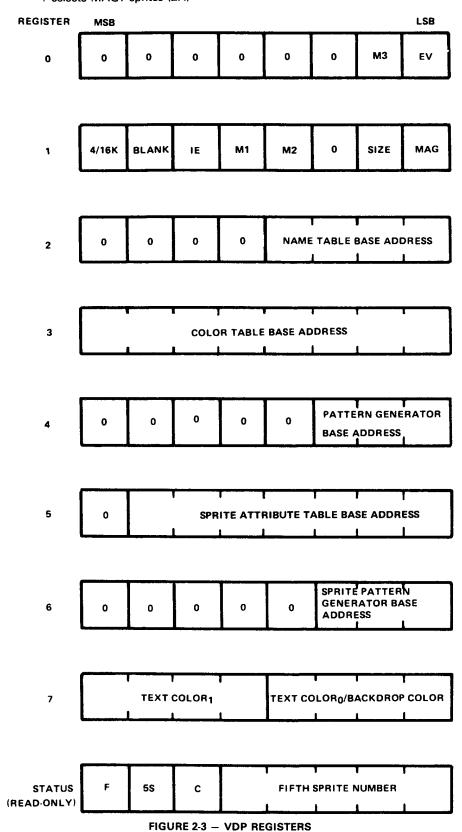

The eight VDP write-only registers are shown in Figure 2-3. They are loaded by the CPU as described in Section 2.1.2. Registers 0 and 1 contain flags to enable or disable various VDP features and modes. Registers 2 through 6 contain values that specify starting locations of various sub-blocks of VRAM. The definitions of these sub-blocks are described in Section 2.4. Register 7 is used to define backdrop and text colors.

Each register is described in the following paragraphs.

#### 2.2.1 Register 0

Register 0 contains two VDP option control bits. All other bits are reserved for future use and must be 0s.

BIT 6 M3 (mode bit 3) (see Section 2.3.2 for table and description)

BIT 7 External VDP enable/disable

0 disables external VDP input1 enables external VDP input

#### **NOTE**

Enabling bit 7 in the TMS9928A/9929A causes A-Y and B-Y to go to the sync level only when all planes in front of the pixel under question are transparent.

#### 2.2.2 Register 1 (contains 8 VDP option control bits)

BIT 0 4/16K selection

0 selects 4027 RAM operation 1 selects 4108/4116 RAM operation

BIT 1 BLANK enable/disable

0 causes the active display area to blank

1 enables the active display

Blanking causes the display to show border color only

BIT 2 IE (Interrupt Enable)

0 disables VDP interrupt

1 enables VDP interrupt

BIT 3,4 M1, M2 (mode bits 1 and 2)

M1, M2 and M3 determine the operating mode of the VDP:

| M1 | M2 | M3 |                  |

|----|----|----|------------------|

| 0  | 0  | 0  | Graphics I mode  |

| 0  | 0  | 1  | Graphics II mode |

| 0  | 1  | 0  | Multicolor Mode  |

| 1  | 0  | 0  | Text mode        |

BIT 5 Reserved

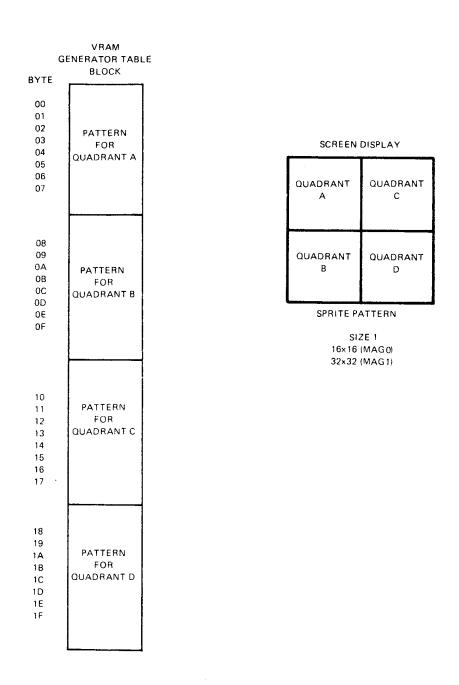

#### BIT 6 Size (sprite size select)

0 selects Size 0 sprites (8  $\times$  8 bit) 1 selects Size 1 sprites (16  $\times$  16 bits)

#### BIT 7 MAG (Magnification option for sprites)

0 selects MAG0 sprites (1X)

1 selects MAG1 sprites (2X)

#### 2.2.3 Register 2

Register 2 defines the base address of the Name Table sub-block. The range of its contents is from 0 to 15. The contents of the register form the upper 4 bits of the 14-bit Name Table addresses; thus the Name Table base address is equal to (Register 2) \*400(hex).

#### 2.2.4 Register 3

Register 3 defines the base address of the Color Table sub-block. The range of its contents is from 0 to 255. The contents of the register form the upper 8 bits of the 14-bit Color Table addresses; thus the Color Table base address is equal to (Register 3) \*40(hex).

#### 2.2.5 Register 4

Register 4 defines the base address of the Pattern, Text or Multicolor Generator sub-block. The range of its contents is 0 through 7. The contents of the register form the upper 3 bits of the 14-bit Generator addresses; thus the Generator base address is equal to (Register 4) \*800(hex).

#### 2.2.6 Register 5

Register 5 defines the base address of the Sprite Attribute Table sub-block. The range of its contents is from 0 through 127. The contents of the register form the upper 7 bits of the 14-bit Sprite Attribute Table addresses; thus the base address is equal to (Register 5) \*80(hex).

#### 2.2.7 Register 6

Register 6 defines the base address of the Sprite Pattern Generator sub-block. The range of its contents is 0 through 7. The contents of the register form the upper 3 bits of the 14-bit Sprite Pattern Generator addresses; thus the Sprite Pattern Generator base address is equal to (Register 6) \*800(hex).

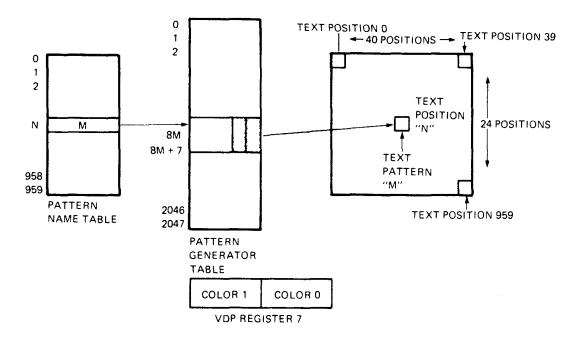

#### 2.2.8 Register 7

The upper 4 bits of Register 7 contain the color code of color 1 in the Text mode. The lower 4 bits contain the color code for color 0 in the Text mode and the backdrop color in all modes.

#### 2.2.9 Setup Values for VDP Registers 2 through 6.

#### VRAM TABLE ADDRESSING

Register 2 in the VDP contains the starting address for the Name Table sub-block.

$$R2 * 400(16) = START ADDRESS$$

| R2 | ADDRESS                          |   |

|----|----------------------------------|---|

| 00 | 0000                             |   |

| 01 | 0400                             |   |

| 02 | 0800                             |   |

| 03 | 0C00 - MAXIMUM NUMBER FOR 4K RAM | S |

| 04 | 1000                             |   |

| 05 | 1400                             |   |

| 06 | 1800                             |   |

| 07 | 1C00                             |   |

| 80 | 2000                             |   |

| 09 | 2400                             |   |

| 0A | 2800                             |   |

| 0B | 2C00                             |   |

| OC | 3000                             |   |

| 0D | 3400                             |   |

| 0E | 3800                             |   |

| 0F | 3C00 - MAXIMUM NUMBER            |   |

(R3) \* 40(16) STARTING ADDRESS

| <u> </u> | 07407         | II .     | 07457   | 11 | 1       |

|----------|---------------|----------|---------|----|---------|

| R3       | START ADDRESS |          | START   |    | START   |

| 00       | 0000          | R3 28    | ADDRESS | R3 | ADDRESS |

| 01       | 0040          | 28       | 0A00    | 50 | 1400    |

| 02       | 0080          | 29<br>2A | 0A40    | 51 | 1440    |

| 03       | E .           | 2A<br>2B | 0A80    | 52 | 1480    |

| 03       | 0000          | 2B<br>2C | 0AC0    | 53 | 14C0    |

| 05       | 0100          | 13       | 0B00    | 54 | 1500    |

| 06       | 0140          | 2D       | 0B40    | 55 | 1540    |

| 07       | 0180          | 2E       | 0B80    | 56 | 1580    |

| 08       | 01C0          | 2F       | 0BC0    | 57 | 15C0    |

| 09       | 0200          | 30       | 0C00    | 58 | 1600    |

|          | 0240          | 31       | 0C40    | 59 | 1640    |

| OA<br>OB | 0280          | 32       | 0C80    | 5A | 1680    |

| OC OB    | 02C0          | 33       | 0CC0    | 5B | 16C0    |

| 1        | 0300          | 34       | 0D00    | 5C | 1700    |

| 0D       | 0340          | 35       | 0D40    | 5D | 1740    |

| 0E       | 0380          | 36       | 0D80    | 5E | 1780    |

| 0F       | 03C0          | 37       | 0DC0    | 5F | 17C0    |

| 10       | 0400          | 38       | 0E00    | 60 | 1800    |

| 11       | 0440          | 39       | 0E40    | 61 | 1840    |

| 12       | 0480          | 3A       | 0E80    | 62 | 1880    |

| 13       | 04C0          | 3B       | 0EC0    | 63 | 18C0    |

| 14       | 0500          | 3C       | 0F00    | 64 | 1900    |

| 15       | 0540          | 3D       | 0F40    | 65 | 1940    |

| 16       | 0580          | 3E       | 0F80    | 66 | 1980    |

| 17       | 05C0          | 3F       | 0FC0*   | 67 | 19C0    |

| 18       | 0600          | 40       | 1000    | 68 | 1A00    |

| 19       | 0640          | 41       | 1040    | 69 | 1A40    |

| 1A       | 0680          | 42       | 1080    | 6A | 1A80    |

| 1B       | 06C0          | 43       | 10C0    | 6B | 1AC0    |

| 1C       | 0700          | 44       | 1100    | 6C | 1B00    |

| 1D       | 0740          | 45       | 1140    | 6D | 1B40    |

| 1E       | 0780          | 46       | 1180    | 6E | 1B80    |

| 1F       | 07C0          | 47       | 11C0    | 6F | 1BC0    |

| 20       | 0800          | 48       | 1200    | 70 | 1C00    |

| 21       | 0840          | 49       | 1240    | 71 | 1C40    |

| 22       | 0880          | 4A       | 1280    | 72 | 1C80    |

| 23       | 08C0          | 4B       | 12C0    | 73 | 1CC0    |

| 24       | 0900          | 4C       | 1300    | 74 | 1D00    |

| 25       | 0940          | 4D       | 1340    | 75 | 1D40    |

| 26       | 0980          | 4E       | 1380    | 76 | 1D80    |

| 27       | 09C0          | 4F       | 13C0    | 77 | 1DC0    |

<sup>\*</sup>Maximum number for 4K RAMS

(R3)\* 40(16) STARTING ADDRESS (Concluded)

|            | START   |    | START   |          | START   |

|------------|---------|----|---------|----------|---------|

| R3         | ADDRESS | R3 | ADDRESS | R3       | ADDRESS |

| 78         | 1E00    | A6 | 2980    | D3       | 34C0    |

| 79         | 1E40    | A7 | 29C0    | D4       | 3500    |

| 7A         | 1E80    | A8 | 2A00    | D5       | 3540    |

| 7B         | 1EC0    | A9 | 2A40    | D6       | 3580    |

| 7C         | 1F00    | AA | 2A80    | D7       | 35C0    |

| 7D         | 1F40    | AB | 2AC0    | D8       | 3600    |

| 7E         | 1F80    | AC | 2B00    | D9       | 3640    |

| 7 <b>F</b> | 1FC0    | AD | 2B40    | DA       | 3680    |

| 80         | 2000    | AE | 2B80    | DB       | 36C0    |

| 81         | 2040    | AF | 2BC0    | DC       | 3700    |

| 82         | 2080    | В0 | 2C00    | DD       | 3740    |

| 83         | 20C0    | B1 | 2C40    | DE       | 3780    |

| 84         | 2100    | B2 | 2C80    | DF       | 37C0    |

| 85         | 2140    | В3 | 2CC0    | EO       | 2800    |

| 86         | 2180    | B4 | 2D00    | E1       | 3840    |

| 87         | 21C0    | 85 | 2D40    | E2       | 3880    |

| 88         | 2200    | B6 | 2D80    | E3       | 38C0    |

| 89         | 2240    | B7 | 2DC0    | E4       | 3900    |

| 8A         | 2280    | В8 | 2E00    | E5       | 3940    |

| 8B         | 22C0    | B9 | 2E40    | E6       | 3980    |

| 8C         | 2300    | ВА | 2E80    | E7       | 39C0    |

| 8D         | 2340    | BB | 2EC0    | E8       | 3A00    |

| 8E         | 2380    | ВС | 2F00    | E9       | 1A40    |

| 8F         | 23C0    | BD | 2F40    | EA       | 3A80    |

| 90         | 2400    | BE | 2F80    | ЕB       | 3AC0    |

| 91         | 2440    | BF | 2FC0    | EC       | 3B00    |

| 92         | 2480    | CO | 3000    | ED       | 3B40    |

| 93         | 24C0    | C1 | 3040    | EE       | 3B80    |

| 94         | 2500    | C2 | 3080    | EF       | 3BCD    |

| 95         | 2540    | СЗ | 30C0    | F0       | 3C00    |

| 96         | 2580    | C4 | 3100    | F1       | 3C40    |

| 97         | 25C0    | C5 | 3140    | F2       | 3C80    |

| 98         | 2600    | C6 | 3180    | F3       | 3CC0    |

| 99         | 2640    | C6 |         | F4       |         |

| 9A         | 2680    | 1  | 31C0    | 1        | 2D00    |

| 9B         | 26C0    | C8 | 3200    | F5       | 3D40    |

| 9C         | 2700    | C9 | 3240    | F6       | 3D80    |

| 9D         | 2740    | CA | 3280    | F7       | 3DC0    |

| 9E         | 2780    | CB | 32C0    | F8       | 3E00    |

| 9F         | 27C0    | CC | 3300    | F9       | 3E40    |

| A0         | 2800    | CD | 3340    | FA       | 3E80    |

| A1         | 2840    | CE | 3380    | FB       | 3EC0    |

| A2         | 2880    | CF | 33C0    | FC       | 3F00`   |

| A3         | 28C0    | D0 | 3400    | FD       | 3F40    |

| A4         | 2900    | D1 | 3440    | FE       | 3F80    |

| A5         | 2940    | D2 | 3480    | FF       | 3FC0    |

| L          |         | l  |         | <u> </u> |         |

Register 4 in the VDP contains the starting address for the Pattern Generator Sub-block.

(R4) \* 800<sub>(16)</sub> = START ADDRESS

| R4 | START<br>ADDRESS          |

|----|---------------------------|

| 00 | 0000                      |

| 01 | 0800 — Max # for 4K RAMS  |

| 02 | 1000                      |

| 03 | 1800                      |

| 04 | 2000                      |

| 05 | 2800                      |

| 06 | 3000                      |

| 07 | 3800 - Max # for 16K RAMS |

Register 5 in the VDP contains the starting address for the Sprite Attribute Table.

(R5) \* 80(16) = START ADDRESS

|          | START        |    | START   |          | START   | П  | START   |

|----------|--------------|----|---------|----------|---------|----|---------|

| R5       | ADDRESS      | R5 | ADDRESS | R5       | ADDRESS | R5 | ADDRESS |

| 00       | 0000         | 21 | 1080    | 40       | 2000    | 60 | 3000    |

| 01       | 0080         | 22 | 1100    | 41       | 2080    | 61 | 3080    |

| 02       | 0400         | 23 | 1180    | 42       | 2100    | 62 | 3100    |

| 03       | 0180         | 24 | 1200    | 43       | 2180    | 63 | 3180    |

| 04       | 0200         | 25 | 1280    | 44       | 2200    | 64 | 3200    |

| 05       | 0280         | 26 | 1300    | 45       | 2280    | 65 | 3280    |

| 06       | 0300         | 27 | 1380    | 46       | 2300    | 66 | 3300    |

| 07       | 0380         | 28 | 1400    | 47       | 2380    | 67 | 3380    |

| 08       | 0400         | 29 | 1480    | 48       | 2400    | 68 | 3400    |

| 09       | 0480         | 2A | 1500    | 49       | 2480    | 69 | 3480    |

| 0A       | 0500<br>0580 | 2B | 1580    | 4A       | 2500    | 6A | 3500    |

| OB<br>OC | 0600         | 2C | 1600    | 4B       | 2580    | 6B | 3580    |

| OD OD    | 0680         | 2D | 1680    | 4C       | 2600    | 6C | 3600    |

| 0E       | 0700         | 2E | 1700    | f I      | 2680    | 6D | 3680    |

| 0F       | 0780         | 2F | 1780    | 4D<br>4E | 2700    | 6E | 3700    |

| 10       | 0800         | ì  |         | 4E<br>4F | 2780    | 6E | 3780    |

| 11       | 0880         | 30 | 1800    | 50       | 2800    | 70 | 3800    |

| 12       | 0900         | 31 | 1880    | 50       | 2880    | 70 | 3880    |

| 13       | 0980         | 32 | 1900    | 52       | 2900    | 72 | 3900    |

| 14       | 0A00         | 33 | 1980    | 53       | 2980    | 73 | 3980    |

| 15       | 0A80         | 34 | 1A00    | 54       | 2A00    | 74 | 3A00    |

| 16       | 0В00         | 35 | 1A80    | 55       | 2A80    | 75 | 3A80    |

| 17       | 0B80         | 36 | 1B00    | 56       | 2B00    | 76 | 3B00    |

| 18       | 0C00         | 37 | 1B80    | 57       | 2B80    | 77 | 3B80    |

| 19       | 0C80         | 38 | 1C00    | 58       | 2C00    | 78 | 3C00    |

| 1A       | 0D00         | 39 | 1C80    | 59       | 2C80    | 79 | 3C80    |

| 1B       | 0D80         | 3A | 1D00    | 5A       | 2D00    | 7A | 3D00    |

| 1C       | 0E00         | 3B | 1D80    | 5B       | 2D80    | 7B | 3D80    |

| 1D       | 0E80         | 3C | 1E00    | 5C       | 2E00    | 7C | 3E00    |

| 1E       | 0F00         | 3D | 1E80    | 5D       | 2E80    | 7D | 3E80    |

| 1F       | 0F80 *       | 3E | 1F00    | 5E       | 2F00    | 7E | 3F00    |

| 20       | 1000         | 3F | 1F80    | 5F       | 2F80    | 7F | 3F80    |

|          |              |    |         |          |         |    |         |

<sup>\*</sup>Maximum number for 4K RAMS

Register 6 contains the value for the starting address of the Sprite Pattern Generator sub-block. STARTING ADDRESS = R6 \*< 800

| R6 | START<br>ADDRESS |                    |

|----|------------------|--------------------|

| 00 | 0000             |                    |

| 01 | 0800 -           | Max # for 4K DRAMS |

| 02 | 1000             |                    |

| 03 | 1800             |                    |

| 04 | 2000             |                    |

| 05 | 2800             |                    |

| 06 | 3000             |                    |

| 07 | 3800 —           | Max # for 16K RAMS |

#### 2.3 STATUS REGISTER

The VDP has a single 8-bit status register that can be accessed by the CPU. The status register contains the interrupt pending flag, the sprite coincidence flag, the fifth sprite flag, and the fifth sprite number, if one exists. The format of the status register is shown in Figure 2-3 and is discussed in the following paragraphs.

The status register may be read at any time to test the F, C, and 5S status bits. Reading the status register will clear the interrupt flag, F. However, asynchronous reads will cause the frame flag (F) bit to be reset and therefore missed. Consequently, the status register should be read only when the VDP interrupt is pending.

#### 2.3.1 Interrupt Flag (F)

The F status flag in the status register is set to 1 at the end of the raster scan of the last line of the active display. It is reset to a 0 after the status register is read or when the VDP is externally reset. If the Interrupt Enable bit in VDP Register 1 is active (1), the VDP interrupt output (INT) will be active (low) whenever the F status flag is a 1.

Note that the status register needs to be read frame by frame in order to clear the interrupt and receive the new interrupt of the next frame.

#### 2.3.2 Coincidence Flag (C)

The C status flag in the status register is set to a 1 if two or more sprites coincide. Coincidence occurs if any two sprites on the screen have one overlapping pixel. Transparent colored sprites, as well as those that are partially or completely off the screen, are also considered. Sprites beyond the Sprite Attribute Table terminator (D016) are not considered. The C flag is cleared to a 0 after the status register is read or the VDP is externally reset. The status register should be read immediately upon powerup to ensure that the coincidence flag is reset.

The VDP checks each pixel position for coincidence during the generation of the pixel regardless of where it is located on the screen. This occurs every 1/60th of a second for the TMS9918A and TMS9928A and every 1/50th of a second for the TMS9929A. Thus, when moving sprites more than one pixel position during these intervals, it is possible for the sprites to have multiple pixels overlapping or even to have passed completely over one another when the VDP checks for coincidence.

## 2.3.3 Fifth Sprite Flag (5S) and Number

The 5S status flag in the status register is set to a 1 whenever there are five or more sprites on a horizontal line (lines 0 to 192) and the frame flag is equal to a 0. The 5S status flag is cleared to a 0 after the status register is read or the VDP is externally reset. The number of the fifth sprite is placed into the lower 5 bits of the status register when the 5S flag is set and is valid whenever the 5S flag is 1. The setting of the fifth sprite flag will not cause an interrupt.

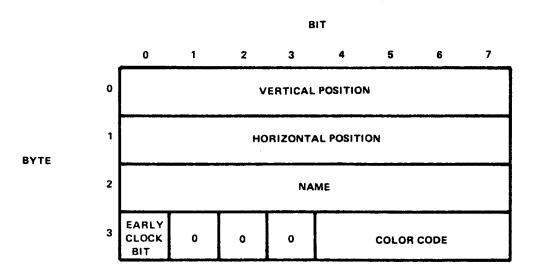

#### 2.4 VIDEO DISPLAY MODES

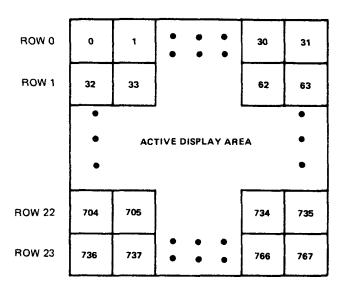

The VDP displays an image on the screen that can best be envisioned as a set of display planes sandwiched together. Figure 2-4 shows the definition of each of the planes. Objects on planes closest to the viewer have higher priority. In cases where two entities on two different planes are occupying the same spot on the screen, the entity on the higher priority plane will show at that point. For an entity on a specific plane to show through, all planes in front of that plane must be transparent at that point. The first 32 planes (Figure 2-5) each may contain a single sprite. The areas of the Sprite Planes, outside of the sprite itself, are transparent. Since the coordinates of the sprite are in terms of pixels, the sprite can be positioned and moved about very accurately. Sprites are available in three sizes:  $8 \times 8$  pixels,  $16 \times 16$  pixels, and  $32 \times 32$  pixels.

Behind the Sprite Planes is the Pattern Plane. The Pattern Plane is used for textual and graphics images generated by the Text, Graphics I, Graphics II, or Multicolor modes. Behind the Pattern Plane is the backdrop, which is larger in area than the other planes so that it forms a border around the other planes. The last and lowest priority plane is the External VDP Plane. Its image is defined by the external VDP input pin which allows the TMS9918A to mix the external video signal internal to the chip.

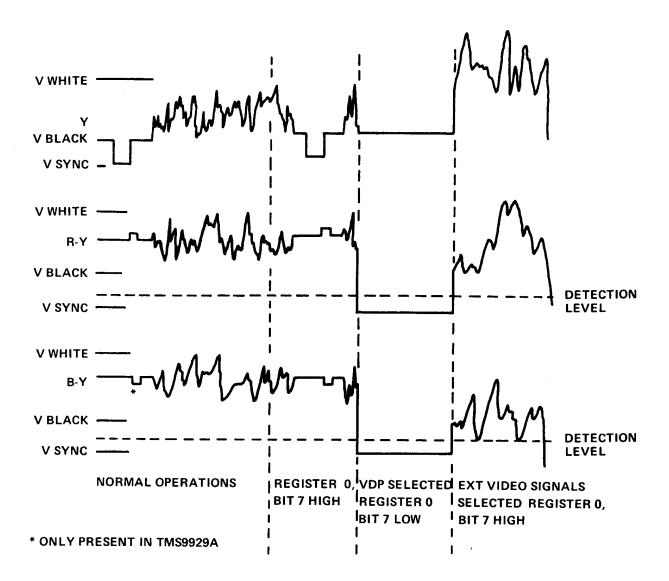

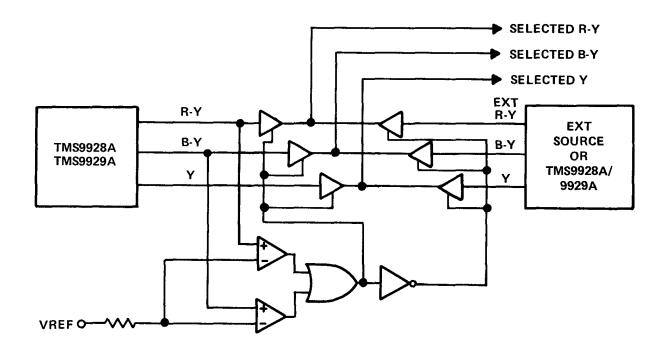

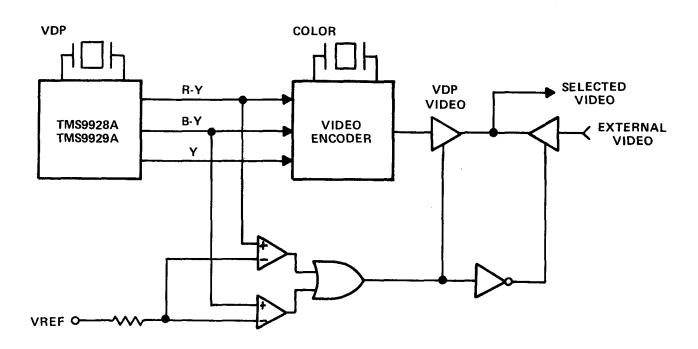

This mixing must occur outside of the chip for the TMS9928A and TMS9929A. This is achieved through the color difference outputs swinging to a special level (sync level is shown in Figure 2-6) not used by the color difference signals in normal operation. This occurs when bit 7 of Register 0 is set high. External mixing circuitry is required to detect this change in the level of the color difference signals and then switch from the VDP signals to an external source's signals (see Figures 2-7 and 2-8).

FIGURE 2-4 - VDP DISPLAY PLANES (DEFINITION)

FIGURE 2-5 — VDP DISPLAY PLANES (FIRST 32 PLANES)

FIGURE 2-6 - TMS9928A/9929A SIGNAL WAVEFORMS FOR MULTIPLE VDP OPERATION

FIGURE 2-7 — USING COLOR DIFFERENCE SIGNALS TO MIX EXTERNAL COLOR DIFFERENCE TYPE SOURCE

FIGURE 2-8 — USING COLOR DIFFERENCE SIGNALS TO MIX EXTERNAL VIDEO SOURCES

The backdrop consists of a single color used for the display borders and as the default color for the active display area. The default color is stored in the VDP Register 7. When the backdrop color register contains the transparent code, the backdrop automatically defaults to black if the external VDP mode is not selected.

The 32 Sprite Planes are used for the 32 sprites in the Multicolor and Graphics modes. They are not used in the Text mode and are automatically transparent. Each of the sprites can cover an  $8\times 8$ ,  $16\times 16$ , or  $32\times 32$  pixel area on its plane. Any part of the plane not covered by the sprite is transparent. All or part of each sprite may also be transparent. Sprite 0 is on the outside or highest plane, and sprite 31 is on the plane immediately adjacent to Pattern Plane. Whenever a pixel in a Sprite Plane is transparent, the color of the next plane can be seen through that plane. If, however, the sprite pixel is non-transparent, the colors of the lower planes are automatically replaced by the sprite color.

There is also a restriction on the number of sprites on a line. Only four sprites can be active on any horizontal line. Additional sprites on a line will be automatically made transparent for that line. Only those sprites that are active on the display will cause the coincidence flag to set. The VDP status register provides a flag bit and the number of the fifth sprite whenever this occurs. The Pattern Plane is used in the Text, Multicolor, and Graphics modes for display of the graphic patterns of characters. Whenever a pixel on the Pattern Plane is nontransparent, the backdrop color is automatically replaced by the Pattern Plane color. When a pixel in the Pattern Plane is transparent, the backdrop color can be seen through the Pattern Plane.

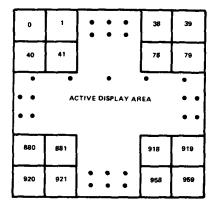

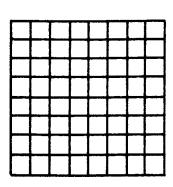

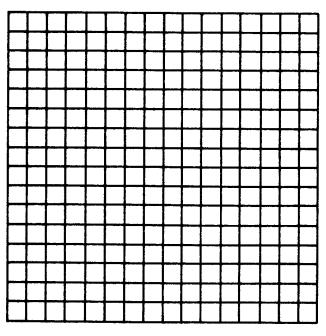

The VDP has four video color display modes that appear on the Pattern Plane: Graphics I mode, Graphics II mode, Text mode, and Multicolor mode. Graphics I and Graphics II modes cause the Pattern Plane to be broken up into groups of 8  $\times$  8 pixels, called pattern positions. Since the full image is 256  $\times$  192 pixels, there are 32  $\times$  24 pattern positions on the screen in the Graphics modes.

In Graphics I mode, 256 possible patterns may be defined for the 768 pattern positions with two unique colors allowed for each line of a pattern definition. Thus, all 15 colors plus transparent may be used in a single pattern position.

In Text mode, the Pattern Plane is broken into groups of  $6 \times 8$  pixels, called text positions. There are  $40 \times 24$  text positions on the screen in this mode. In Text mode, sprites do not appear on the screen and two colors are defined for the entire screen by VDP Register 7.

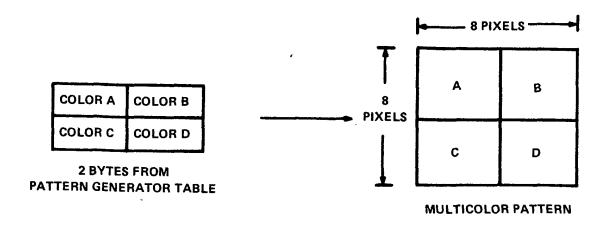

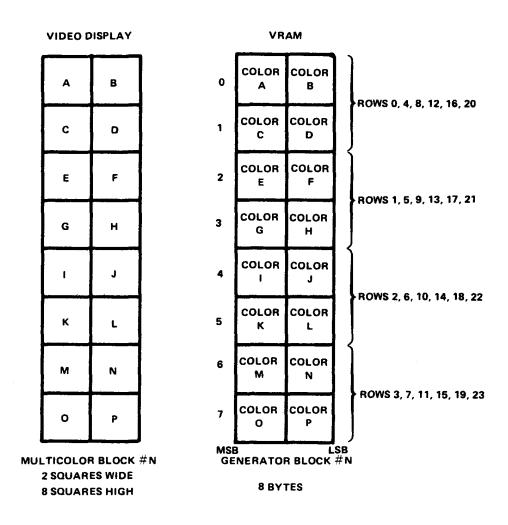

In Multicolor mode, the screen is broken into a grid of  $64 \times 48$  positions, each of which is a  $4 \times 4$  pixel. Within each position, one unique color is allowed.

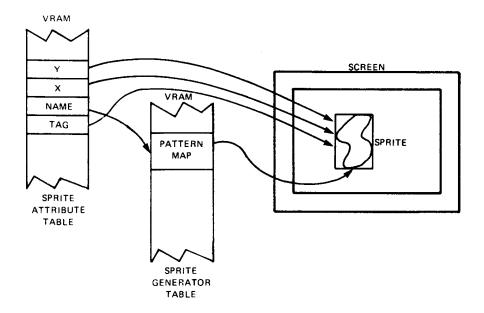

The VDP registers define the base addresses for several sub-blocks within VRAM. These sub-blocks form tables which are used to produce the desired image on the TV screen. The Sprite Pattern Generator Table and the Sprite Attribute Table are used to form sprites. The contents of these tables must all be provided by the microprocessor. Animation is achieved by altering the contents of VRAM in real time.

The VDP can display the 15 colors shown in Table 2-3. The VDP colors also provide eight different gray levels for displays on monochrome television; the luminance value in the table indicates these levels, 0.00 being black and 1.00 being white. All other values in the table are expressed as percentages of the white/black voltage swing.

#### NOTE

The gray levels differ slightly for the TMS9918A when compared to the TMS9928A/9929A.

Whenever all planes are of the transparent color at a given point, and external video is not selected, the color shown at that point will be black.

**TABLE 2-3 -- COLOR ASSIGNMENTS**

| ,            |                | TN                         | 1S <b>9</b> 918A          | TMS9928A/9929A |                                |         |  |  |

|--------------|----------------|----------------------------|---------------------------|----------------|--------------------------------|---------|--|--|

| COLOR<br>HEX | COLOR          | LUMINANCE<br>(DC)<br>VALUE | CHROMINANCE<br>(AC VALUE) | Y              | COLOR<br>DIFFERENCE<br>R-Y B-Y |         |  |  |

| 0            | TRANSPARENT    | 0.00                       | _                         | I _            | _                              | _       |  |  |

| 1            | BLACK          | 0.00                       | <u>-</u>                  | 0.00           | .47                            | .47     |  |  |

| 2            | MEDIUM GREEN   | .53                        | .53                       | .53            | .07                            | .20     |  |  |

| 2<br>3       | LIGHT GREEN    | .67                        | .40                       | .67            | .17                            | .27     |  |  |

| 4            | DARK BLUE      | .40                        | .60                       | .40            | .4                             | 1.00    |  |  |

| 5<br>6       | LIGHT BLUE     | .53                        | .53                       | .53            | .43                            | .93     |  |  |

| 6            | DARK RED       | .47                        | .47                       | .47            | .83                            | .30     |  |  |

| 7            | CYAN           | .67                        | .60                       | .73            | 0.00                           | .70     |  |  |

| 8<br>9       | MEDIUM RED     | .53                        | .60                       | .53            | .93                            | .27     |  |  |

| 9            | LIGHT RED      | .67                        | .60                       | .67            | .93                            | .27     |  |  |

| Α            | DARK YELLOW    | .73                        | .47                       | .73            | .57                            | .07     |  |  |

| В            | LIGHT YELLOW   | .80                        | .33                       | .80            | .57                            | .17     |  |  |

| С            | DARK GREEN     | .46                        | .47                       | .47            | .13                            | .23     |  |  |

| D            | MAGENTA        | .53                        | .40                       | .53            | .73                            | .67     |  |  |

| E<br>F       | GRAY           | .80                        | -                         | .80            | .47                            | .47     |  |  |

| F            | WHITE          | 1.00                       | _                         | 1.00           | .47                            | .47     |  |  |

| -            | BLACK LEVEL    | 0.00                       | -                         | 0.00           | .47                            | .47     |  |  |

| -            | COLOR BURST    | 0.00                       | .40                       | 0.00           | 47(28A)                        | .1(28A) |  |  |

|              |                |                            |                           |                | 73(29A)                        | .2(29A) |  |  |

| <del>-</del> | SYNC LEVEL     | -0.40                      | _                         | 46             | .47                            | .47     |  |  |

| _            | EXTERNAL VIDEO | -                          | -                         | 0.00           | .47                            | .47     |  |  |

| -            | LEVEL          | _                          | _                         | 0.00           | 46                             | 46      |  |  |

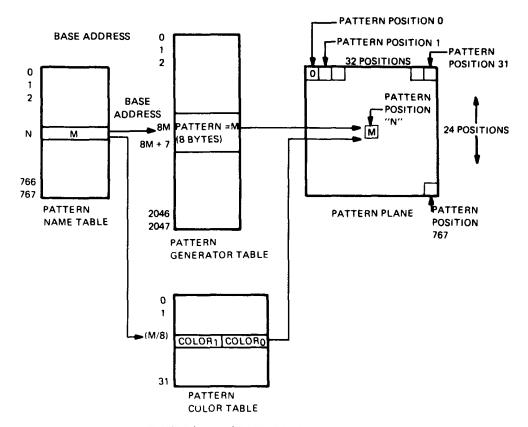

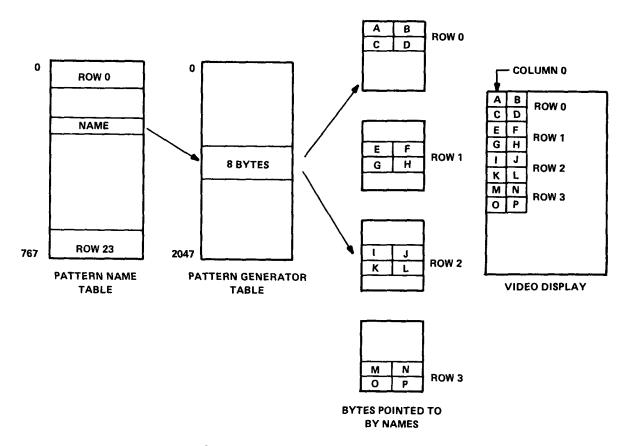

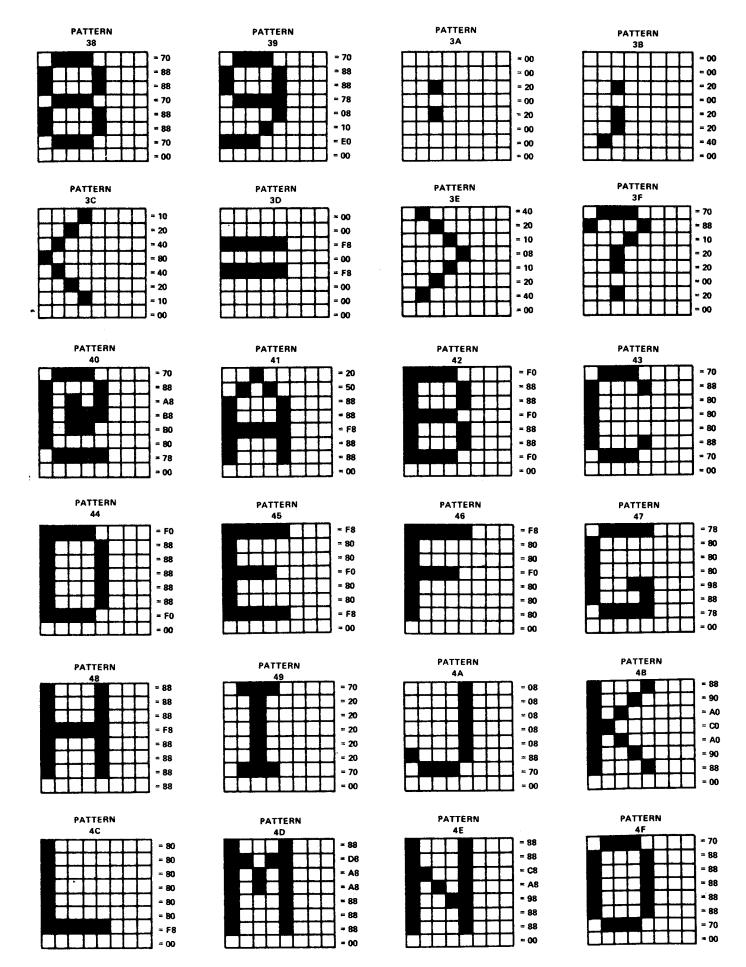

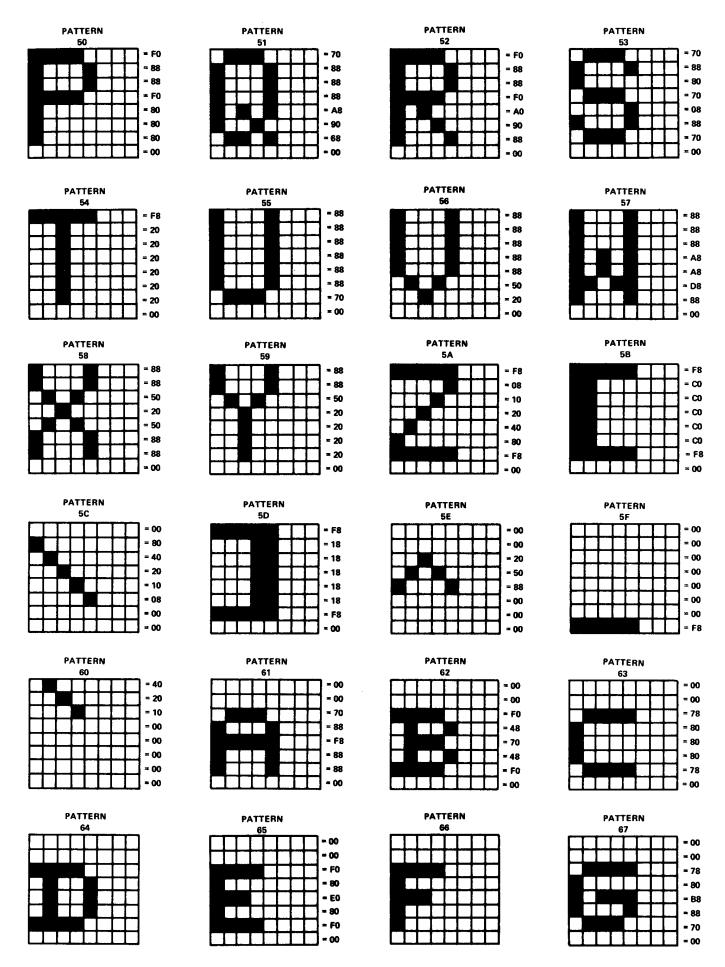

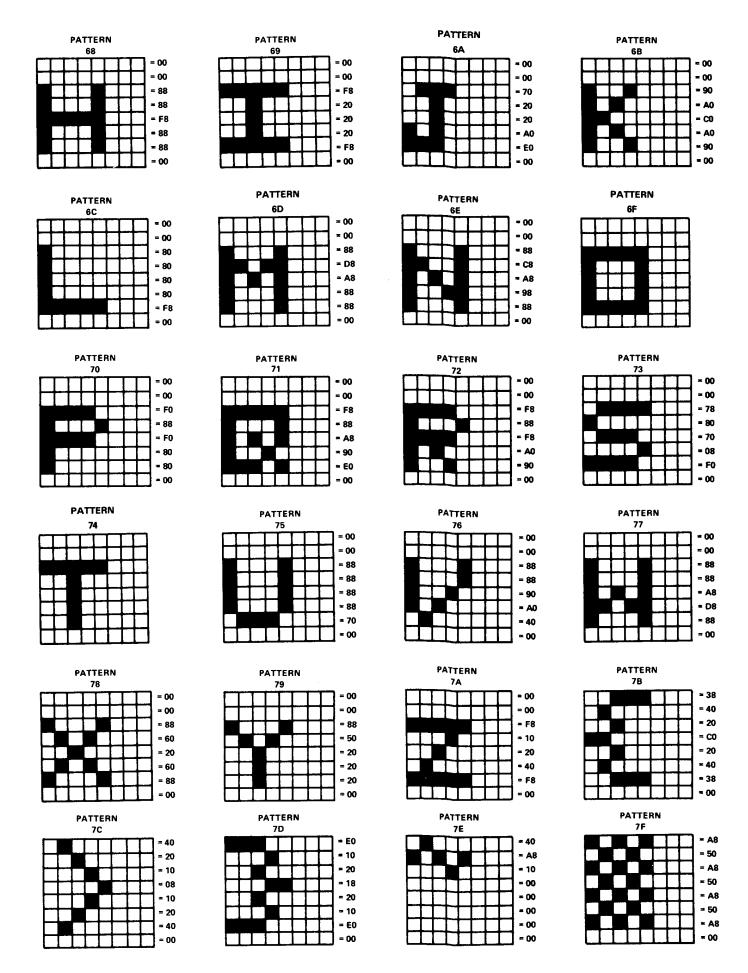

#### 2.4.1 Graphics I Mode

The VDP is in Graphics I mode when M1, M2, and M3 bits in VDP registers 1 and 0 are zero. When in this mode the Pattern Plane is divided into a grid of 32 columns by 24 rows of pattern positions as shown in Figure 2-9). Each of the pattern positions contains  $8 \times 8$  pixel. The tables in VRAM used to generate the Pattern Plane are the Pattern Generator, Name, and Color Tables which require 2848 VRAM bytes. Figure 2-9 illustrates the mapping of these tables into the Pattern Plane. Less memory is required if all 256 possible pattern definitions are not required. The tables can be overlapped to reduce the amount of VRAM needed for pattern generation. Examples of VRAM memory allocation are provided in Section 3.3.

FIGURE 2-9 — PATTERN GRAPHICS NAME TABLE MAPPING

FIGURE 2-10 - GRAPHICS I MODE MAPPING

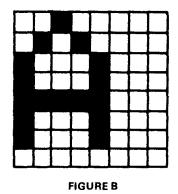

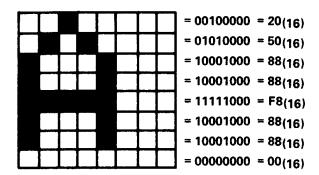

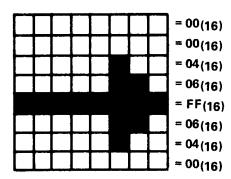

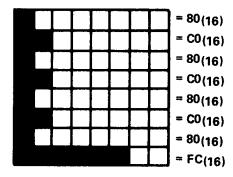

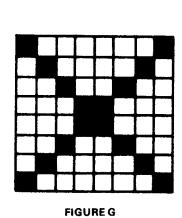

The Pattern Generator Table contains a library of patterns that can be displayed in the pattern positions. It is 2048 bytes long and is arranged into 256 patterns, each of which is 8 bytes long, yielding  $8 \times 8$  bits. All of the 1s in the 8-byte pattern can designate one color (color 1), while all the 0s can designate another color (color 0).

The full 8-bit pattern name is used to select one of the 256 pattern definitions in the Pattern Generator Table. The table is a 2048-byte block in VRAM beginning on a 2-kilobyte boundary. The starting address of the table is determined by the generator base address in VDP Register 4. The base address forms the three MSBs of the 14-bit VRAM address for each Pattern Generator Table entry. The next 8 bits indicate the 8-bit name of the selected pattern definition. The lowest 3 bits of the VRAM address indicate the row number within the pattern definition.

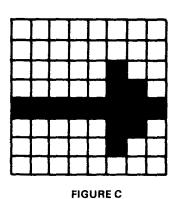

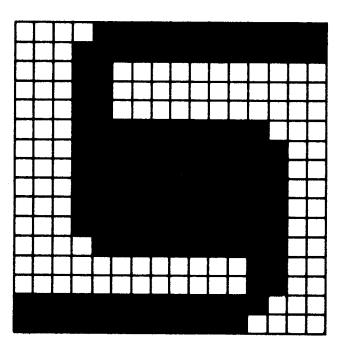

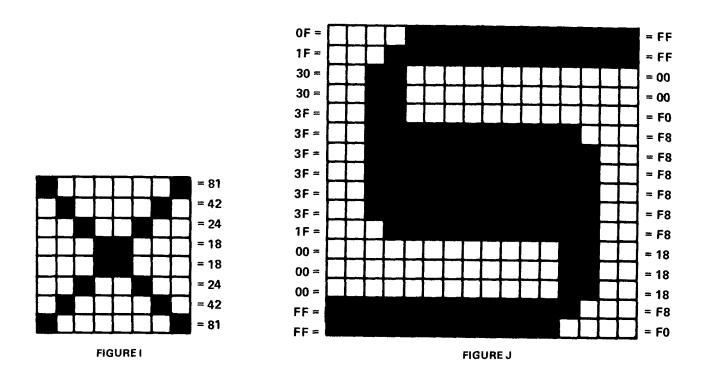

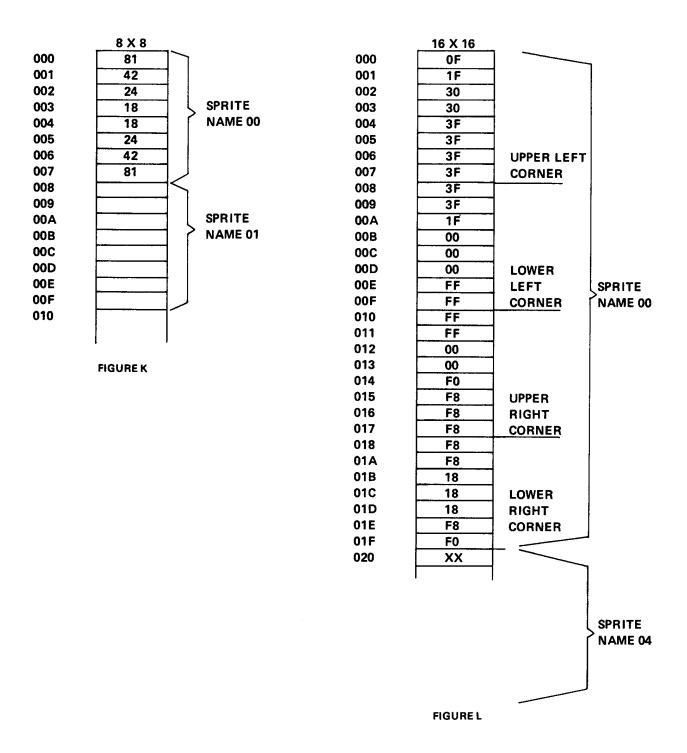

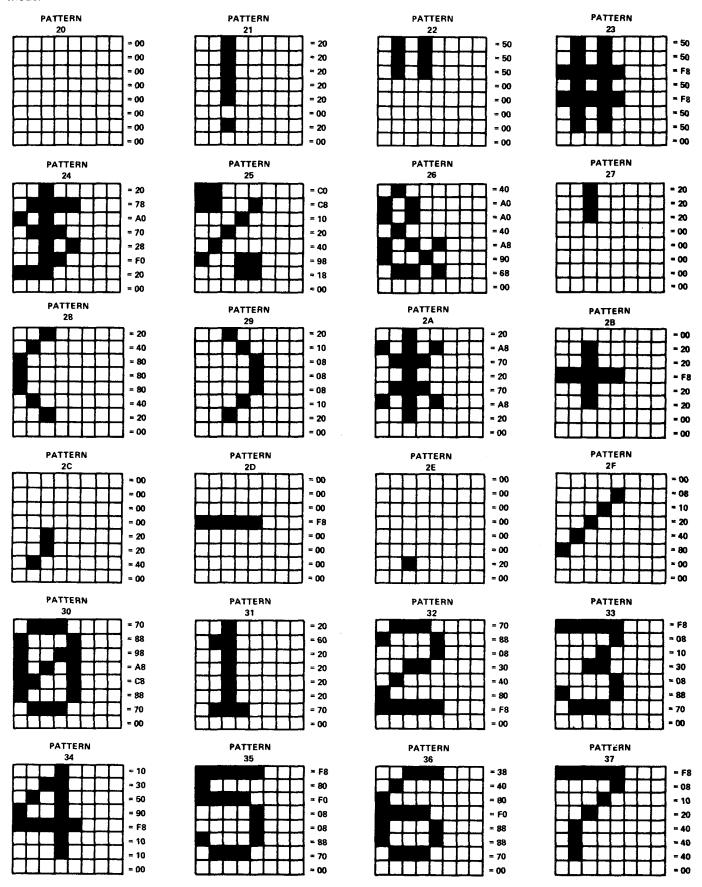

There are 8 bytes required for each of the 256 possible unique  $8 \times 8$  pattern definitions. The first byte defines the first row of the pattern, and the second byte defines the second row. The first bit of each of the eight bytes defines the first column of the pattern. The remaining rows and columns are similarly defined. Each bit entry in the pattern definition selects one of the two colors for that pattern. A 1 bit selects the color code (color 1) contained in the most significant 4 bits of the corresponding color table byte. A 0 bit selects the other color code (color 0). An example of pattern definition mapping is provided in Figure 2-11.

| ROW/BYTE | 1 |    | COL |   |   |   | BIT<br>(PATTERN DEFINITION) |   |   |   |   |   |   |   |     |  |

|----------|---|----|-----|---|---|---|-----------------------------|---|---|---|---|---|---|---|-----|--|

|          | 0 | 1_ | 2   | 3 | 4 | 5 | L                           | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7   |  |

| 0        |   | С  | С   | C | C | С | 1                           | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 ( |  |

| 1        |   |    |     |   |   | С |                             | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0   |  |

| 2        |   |    |     |   |   | С |                             | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0   |  |

| 3        |   |    | С   | С | С | С | •                           | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0   |  |

| 4        |   |    |     |   |   | С |                             | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0   |  |

| 5        |   |    |     |   |   | С |                             | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0   |  |

| 6        |   | С  | С   | С | С | С |                             | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0   |  |

| 7        |   |    |     |   |   |   |                             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |  |

NOTES: VDP register 7 entry: 71<sub>16</sub>.

Color code 7 is cyan (signified above by 'C').

Color code 1 is black (signified above by a space).

Bit 0 is the most significant bit of each data byte.

FIGURE 2-11 - PATTERN DISPLAY MAPPING

The color of the 1s and 0s is defined by the Pattern Color Table that contains 32 entries, each of which is 1 byte long. Each entry defines two colors: the most significant 4 bits of each entry define the color of the 1s, and the least significant 4 bits define the color of the 0s. The first entry in the color table defines the colors for patterns 0 to 7; the next entry for patterns 8 to 15, and so on. (See Table 2-4 for assignments.) Thus, 32 different pairs of colors may be displayed simultaneously.

The Pattern Name Table is located in a contiguous 768-byte block in VRAM beginning on a 1-kilobyte boundary. The starting address of the Name Table is determined by the 4-bit Name Table base address field in VDP Register 2. The base address forms the upper 4 bits of the 14-bit VRAM address. The lower 10 bits of the VRAM address are formed from the row and column counters. An example of pattern name table addressing is given in Section 3.3.

TABLE 2-4 - GRAPHICS | MODE COLOR TABLE

| Byte No. | Pattern No. | Byte No.                                      | Pattern No. |  |  |  |

|----------|-------------|-----------------------------------------------|-------------|--|--|--|

| 0        | 07          | 16                                            | 128., 135   |  |  |  |

| 1        | 1           | 17                                            |             |  |  |  |

| •        | 815         | 1                                             | 136143      |  |  |  |

| 2        | 1623        | 18                                            | 144151      |  |  |  |

| 3        | 2431        | 19                                            | 152159      |  |  |  |

| 4        | 3239        | 20                                            | 160167      |  |  |  |

| 5        | 4047        | 21                                            | 168175      |  |  |  |

| 6        | 4855        | 22                                            | 176183      |  |  |  |

| 7        | 5663        | 23                                            | 184191      |  |  |  |

| 8        | 6471        | 24                                            | 192199      |  |  |  |

| 9        | 7279        | 25                                            | 280207      |  |  |  |

| 10       | 8087        | 26                                            | 208215      |  |  |  |

| 11       | 8895        | 27                                            | 216223      |  |  |  |

| 12       | 96103       | 28                                            | 224231      |  |  |  |

| 13       | 104111      | 29                                            | 232239      |  |  |  |

| 14       | 112119      | 30                                            | 240247      |  |  |  |

| 15       | 120127      | 31                                            | 248-255     |  |  |  |

|          |             | <u>i                                     </u> |             |  |  |  |

Each byte entry in the Name Table is either the name of or the pointer to a pattern definition in the Pattern Generator Table. The upper 5 bits of the 8-bit name identify the color group of the pattern. There are 32 groups of 8 patterns. The same two colors are used for all eight patterns in a group; the color codes are stored in the VDP Color Table. The Color Table is located in a 32-byte clock in VRAM beginning on a 64-byte boundary. The table starting address is determined by the 8-bit Color Table base address in VDP Register 3. The base address forms the upper 8 bits of the 14-bit Color Table entry VRAM address. The next bit is a 0 and the lowest 5 bits are equal to the upper 5 bits of the corresponding Name Table entries.

Since the tables in VRAM have their base addresses defined by the VDP registers, a complete switch of the values in the tables can be made by simply changing the values in the VDP registers. This is especially useful when one wishes to time-slice between two or more screens of graphics.

When the Pattern Generator Table is loaded with a pattern set, manipulation of the Pattern Name Table contents can change the appearance of the screen. Alternatively, a dynamically changing set of patterns throughout the course of a graphics session is easily accomplished since all tables are in VRAM. A total of 2848 VRAM bytes are required for the Pattern, Name, Color and Generator tables. Less memory is needed if all 256 possible pattern definitions are not required; the tables can be overlapped to reduce the amount of VRAM needed for pattern generation. Examples of VRAM memory allocation are provided in Section 3.3.

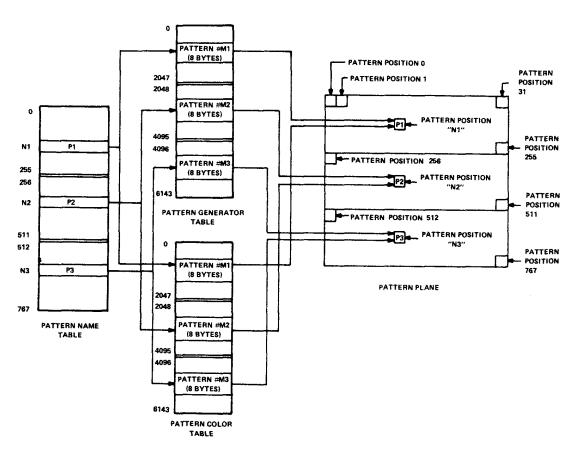

#### 2.4.2 Graphics II Mode

The VDP is in the Graphics II mode bits (M1 = 0, M2 = 0 and M3 = 1). The Graphics II mode is similar to Graphics I mode except it allows a larger library of patterns so that a unique pattern generator entry may be made for each of the 768 (32  $\times$  24) pattern positions on the video screen. Additionally, more color information is included in each 8  $\times$  8 graphics pattern. Thus, two unique colors may be specified for each byte of the 8  $\times$  8 pattern. A larger amount of VRAM (12 kilobytes) is required to implement the full usage of the Graphics II mode.

Like Graphics I mode, the Graphics II mode Pattern Name Table contains 768 entries which correspond to the 768 pattern positions on the display screen. Because the Graphics I mode pattern names are only 8 bits in length, a maximum of 256 pattern definitions may be addressed using the addressing scheme discussed in Section 2.4.10. Graphics II mode, however, segments the display screen into three equal parts of 256 pattern positions each and also segments the Pattern

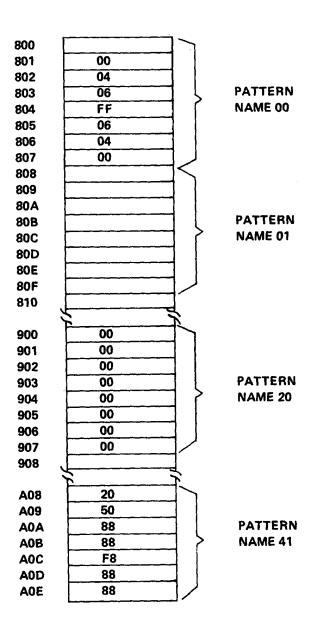

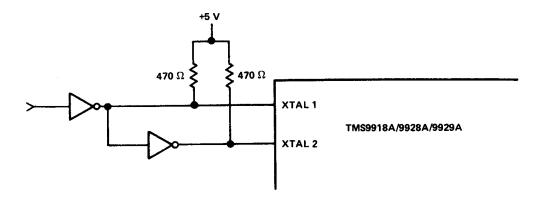

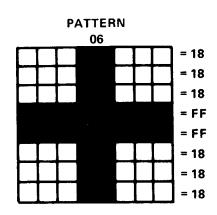

Generator Table into three equal blocks of 2048 bytes each. Pattern definitions in the first third of the display screen correspond to pattern positions in the upper third. Likewise, pattern definitions in the second and third blocks of the Pattern Generator Table correspond to the second and third areas of the Pattern Plane.